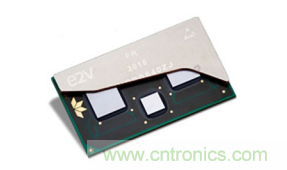

顯然,數(shù)據(jù)轉(zhuǎn)換接收(Rx)系統(tǒng)的核心器件是ADC���。Teledyne e2v在過(guò)去的20多年里一直致力于數(shù)據(jù)轉(zhuǎn)換器技術(shù)的創(chuàng)新��,并提供了多通道�、低噪聲、低失真的微波頻率ADC(如上圖的EV12AQ600)�。這種數(shù)據(jù)轉(zhuǎn)換器使系統(tǒng)設(shè)計(jì)師能(通過(guò)直接RF轉(zhuǎn)換)消除傳統(tǒng)架構(gòu)中下變頻所需的模擬環(huán)節(jié)。利用Teledyne e2v的高端ADC減少模擬環(huán)節(jié)����,并使用高級(jí)的SiP設(shè)計(jì)技術(shù)配合無(wú)需許可證的標(biāo)準(zhǔn)和定制解決方案,設(shè)計(jì)師可以研發(fā)許多標(biāo)準(zhǔn)產(chǎn)品和定制產(chǎn)品���,以滿足特定的性能和/或環(huán)境需求���。

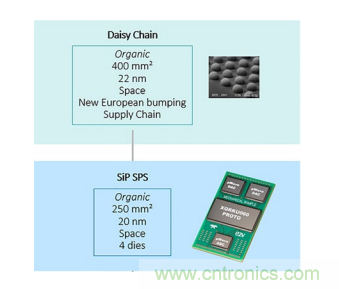

未來(lái)高速SiP直接RF數(shù)據(jù)轉(zhuǎn)換接收(Rx)方案的核心是EV12AQ600。結(jié)合RTH120跟蹤保持放大器(THA)�,PS620實(shí)驗(yàn)SiP RF前端接收板(如下圖所示)的性能非常優(yōu)秀(見第2頁(yè)上器件的核心參數(shù))。EV12AQ600是一款四核ADC�,包含交叉點(diǎn)開關(guān)(CPS)前端,允許四個(gè)ADC核心同時(shí)��、獨(dú)立或成對(duì)地工作����,支持四通道1.6Gsps,兩通道3.2Gsps或單通道6.4Gsps的采樣率��。典型的四通道模式的SFDR(不考慮H2和H3諧波)優(yōu)于70dBFS(-1dBFS輸出,頻率高達(dá)5980MHz)���。

這款器件可提供多種級(jí)別��,包括商業(yè)級(jí)����、工業(yè)級(jí)�����、軍級(jí),最高支持耐輻射宇航級(jí)��。EV12AQ600可用于多種應(yīng)用�����,如高速數(shù)據(jù)采集����、高速測(cè)試儀器�����、自動(dòng)測(cè)試設(shè)備、地球觀測(cè)SAR雷達(dá)載荷、電信MIMO衛(wèi)星載荷���、超寬帶衛(wèi)星數(shù)字接收機(jī)�����、C波段直接RF轉(zhuǎn)換�����、微波軟件定義無(wú)線電����、點(diǎn)對(duì)點(diǎn)微波接收端����、機(jī)器狀態(tài)監(jiān)測(cè)系統(tǒng)、飛行時(shí)間質(zhì)譜分析����、LiDAR、高能物理等��。

器件核心參數(shù)

EV12AQ600 ADC:

• 四個(gè)12-bit 1.6 GSps ADC核心�,支持1��、2或4通

道時(shí)域交織

• 全交織模式采樣率高達(dá)6.4 GSps

• 6.5 GHz輸入帶寬(-3dB)

• 集成的寬帶交叉點(diǎn)開關(guān)

• 支持多通道同步的同步鏈

RTH120 THA:

• 24GHz 輸入帶寬

• 雙THA使輸出保持時(shí)間超過(guò)半個(gè)采樣時(shí)鐘周期

• 全差分設(shè)計(jì)

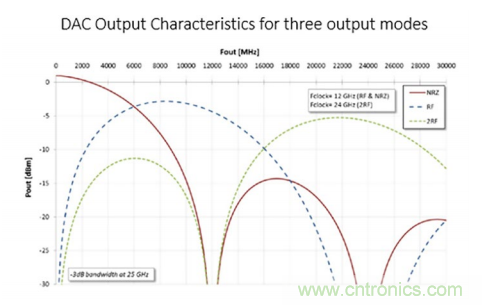

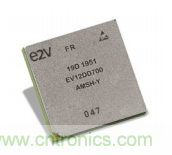

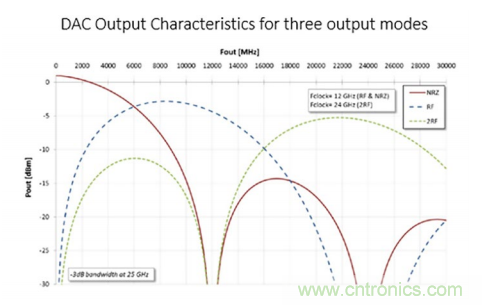

在實(shí)現(xiàn)高速��、最先進(jìn)的SiP數(shù)據(jù)轉(zhuǎn)換發(fā)射端(Tx)解決方案方面��,關(guān)鍵的技術(shù)是EV12DD700(如右圖所示)����。該雙路12位DAC支持高達(dá)12Gsps的采樣率���,可直接產(chǎn)生高達(dá)21GHz的輸出信號(hào),滿刻度階躍響應(yīng)時(shí)間低至15ps�����,在微波頻率的噪聲很低,性能優(yōu)秀����。EV12DD700雙通道DAC也支持Ka波段工作,支持波束形成的應(yīng)用����。這款DAC有25GHz的3dB輸出帶寬,即使超過(guò)25GHz也僅有略大于3dB的衰減(見下圖)���。每個(gè)DAC都集成了一系列復(fù)雜的信號(hào)處理功能,包括一個(gè)用于直接數(shù)字合成(DDS)功能的可編程anti-sinc濾波器�,一個(gè)可編程的復(fù)雜混頻器,以及一個(gè)包含四個(gè)插值環(huán)節(jié)的數(shù)字上變頻器�。數(shù)字處理功能包括:插值(4x, 8x和16x)、帶有數(shù)字控制振蕩器(32位NCO)的數(shù)字上變頻(DUC)�、直接數(shù)字合成(DDS)、數(shù)字波束形成和波束跳變����。DAC的主要功能包括:可編程輸出模式(NRZ, RF, 2RF)、增益調(diào)節(jié)、可編程SINC補(bǔ)償功能和多器件同步。

圖 1

當(dāng)然,所有的高速數(shù)據(jù)轉(zhuǎn)換系統(tǒng)也需要先進(jìn)的數(shù)字處理能力。例如���,Teledyne e2v已經(jīng)認(rèn)證并發(fā)布了一款從NXP最新的Layerscape® 系列篩選出的微處理器LS1046A���,可工作在-55℃到125℃(宇航級(jí)LS1046-Spacce也很快會(huì)發(fā)布)����。LS1046A是NXP的64位ARM® Layerscape產(chǎn)品系列的一款器件��,使用四核ARM® Cortex® A72設(shè)計(jì)�����。

這種設(shè)計(jì)在盡可能小的封裝里實(shí)現(xiàn)了無(wú)與倫比的性能。用戶可以使用與ARM® 技術(shù)兼容的龐大的軟件���、應(yīng)用�、工具的生態(tài)系統(tǒng)。LS1046A是一款1.8GHz的處理器���,集成了包處理加速和高速外設(shè)�����,使用了高性能的架構(gòu),有業(yè)內(nèi)領(lǐng)先的計(jì)算密度。其超過(guò)45,000CoreMarks® 的計(jì)算性能(即30K DMIPS@1.8GHz)���,搭配雙路10Gb以太網(wǎng)、3路PCIe Gen3和1路SATAGen3�,適用于一系列高可靠性的軍用、航空和航天的應(yīng)用�����。LS1046A也集成到了Teledyne e2v最新的Qormino® 計(jì)算模塊中�����,這個(gè)模塊還包含了一個(gè)4GB的DDR4存儲(chǔ)器(見左側(cè)的照片)。此外��,作為Teledyne e2v的半導(dǎo)體生命周期管理計(jì)劃SLiM™的一部分�,這款器件的生命周期可達(dá)15年以上,避免了常見的昂貴的器件過(guò)時(shí)問(wèn)題���。

數(shù)據(jù)轉(zhuǎn)換SiP實(shí)現(xiàn)峰值系統(tǒng)性能:適用于所有細(xì)分市場(chǎng)

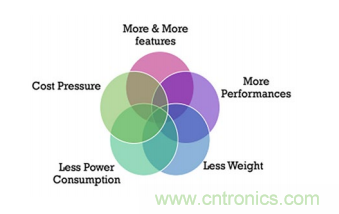

在工業(yè)�����、醫(yī)療�����、飛行電子�����、儀器、電信���、軍事和宇航領(lǐng)域��,數(shù)據(jù)轉(zhuǎn)換系統(tǒng)正在經(jīng)歷快速的變化����。對(duì)于所有的細(xì)分市場(chǎng),首要的系統(tǒng)級(jí)設(shè)計(jì)問(wèn)題是��,如何在模擬和數(shù)字電路之間取得平衡�����,實(shí)現(xiàn)最大的軟件/系統(tǒng)靈活性(從傳感器到計(jì)算機(jī)輸入或從計(jì)算機(jī)輸出到傳感器)��。這個(gè)基本的問(wèn)題要求系統(tǒng)設(shè)計(jì)師劃分(或組合)數(shù)據(jù)轉(zhuǎn)換電路器件�,并結(jié)合模擬和數(shù)字信號(hào)的布線,以實(shí)現(xiàn)多種服務(wù)的軟件最大化��。

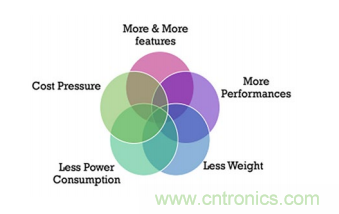

系統(tǒng)工程師了解他們的市場(chǎng)��、應(yīng)用和電路性能的規(guī)范需求���,但設(shè)計(jì)參數(shù)�,例如風(fēng)險(xiǎn)����、技術(shù)選擇、形狀參數(shù)����、開發(fā)時(shí)間表(包括時(shí)間表同步)����、可靠性����,以及與高性能數(shù)據(jù)轉(zhuǎn)換系統(tǒng)相關(guān)的成本,都是高度可變的�����。這些設(shè)計(jì)參數(shù)�,加上不斷變化的系統(tǒng)性能規(guī)格需求,最終導(dǎo)致更窄的設(shè)計(jì)實(shí)現(xiàn)“交集”(圖2)���。

當(dāng)然����,在任何設(shè)計(jì)參數(shù)上犯錯(cuò)誤�,都會(huì)付出巨大的代價(jià)���。因此�,任何可以嵌入到設(shè)計(jì)開發(fā)中的靈活性,只要能為項(xiàng)目增加整體價(jià)值而不是降低價(jià)值����,都是值得投資的。

圖 2 - 不斷增加的設(shè)計(jì)參數(shù)和系統(tǒng)級(jí)性能需求����,產(chǎn)生了更窄的“交集”。

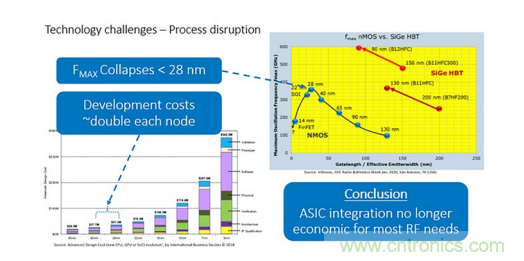

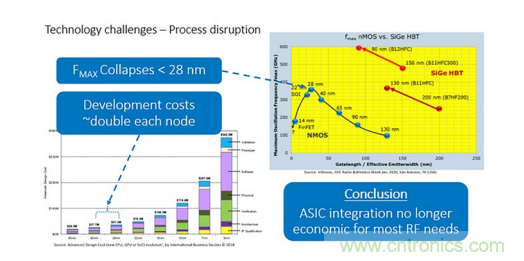

有一個(gè)設(shè)計(jì)參數(shù)可以提高設(shè)計(jì)階段的靈活性���,并最終滿足必要的性能需求�����,特別是對(duì)于數(shù)據(jù)轉(zhuǎn)換系統(tǒng)��。它是利用SiP(系統(tǒng)級(jí)封裝)技術(shù)實(shí)現(xiàn)所需的功能�。過(guò)去���,半導(dǎo)體工藝技術(shù)的不斷進(jìn)步使系統(tǒng)級(jí)設(shè)計(jì)師能夠在SoC(片上系統(tǒng))上實(shí)現(xiàn)完整的電路功能�。隨著門電路長(zhǎng)度縮短至10nm甚至更小��,需要大量數(shù)字計(jì)算的SoC應(yīng)用已可以通過(guò)半導(dǎo)體技術(shù)實(shí)現(xiàn)���。不幸的是����,隨著半導(dǎo)體特征尺寸的減小,芯片的開發(fā)成本呈指數(shù)級(jí)

增長(zhǎng)(見圖3)�����。

圖 3

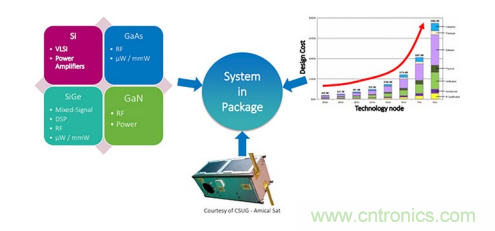

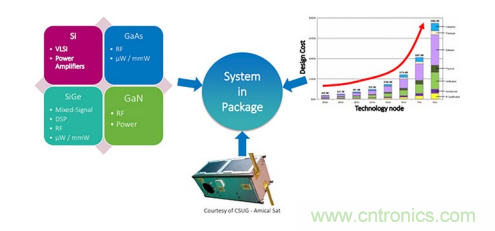

圖3也顯示了最小幾何門尺寸和最大器件振蕩頻率之間的相關(guān)性���。如圖所示�����,F(xiàn)max的拐點(diǎn)在門長(zhǎng)度<28nm的位置�。相應(yīng)的��,隨著門長(zhǎng)度的減小���,開發(fā)成本呈指數(shù)增長(zhǎng)(G=28nm(平均開發(fā)成本5130萬(wàn)美元)����,G=16nm(平均開發(fā)成本1.063億美元)��,G=7nm(成本2.97億美元)���,G=5nm(成本超過(guò)5億美元))��。隨著SoC包含更多的功能����,需要使用更小的門長(zhǎng)度��,其開發(fā)的成本變得令人望而卻步���。例如�,SoC一直是移動(dòng)電話行業(yè)的驅(qū)動(dòng)技術(shù)����,但對(duì)模擬技術(shù)(如MEMS傳感器)的需求不斷增加,導(dǎo)致從SoC到SiP方案的變革�����。圖4說(shuō)明了當(dāng)前推進(jìn)從SoC到SiP的變革的三個(gè)共存的設(shè)計(jì)參數(shù):1)技術(shù):為最優(yōu)系統(tǒng)性能選擇最合適的工藝技術(shù)(即Si�����、GaAs、GaN�����、SiGe等)��,2)小型化���,3)成本����。

圖 4

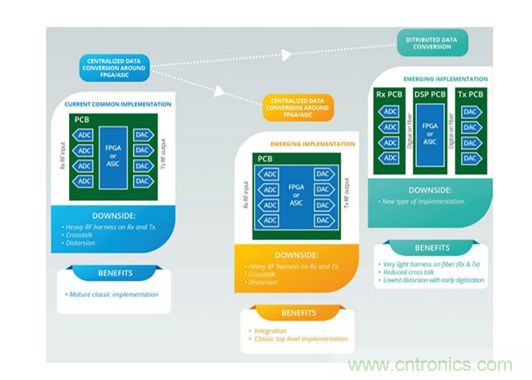

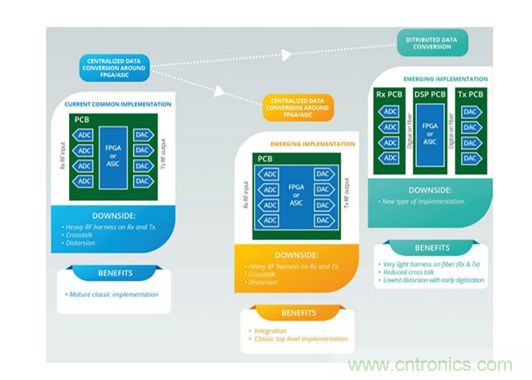

推動(dòng)數(shù)據(jù)轉(zhuǎn)換系統(tǒng)從SoC向SiP發(fā)展的另一個(gè)因素是對(duì)數(shù)據(jù)轉(zhuǎn)換電路器件的劃分(或組合)以及模擬和數(shù)字信號(hào)的布線�,這將允許對(duì)多種服務(wù)進(jìn)行最大程度的軟件化。簡(jiǎn)單來(lái)說(shuō)����,數(shù)據(jù)轉(zhuǎn)換系統(tǒng)可以設(shè)計(jì)為“集中式”或“分隨著SoC包含更多的功能,需要使用更小的門長(zhǎng)度�,其開發(fā)的成本變得令人望而卻步。例如����,SoC一直是移動(dòng)電話行業(yè)的驅(qū)動(dòng)技術(shù),但對(duì)模擬技術(shù)(如MEMS傳感器)的需求不斷增加���,導(dǎo)致從SoC到SiP方案的變革�����。圖4說(shuō)明了當(dāng)前推進(jìn)從SoC到SiP的變革的三個(gè)共存的設(shè)計(jì)參數(shù):1)技術(shù):為最優(yōu)系統(tǒng)性能選擇最合適的工藝技術(shù)(即Si�����、GaAs����、GaN�����、SiGe等)����,2)小型化,3)成本�。

圖 5

因此,Teledyne e2v的高級(jí)的SiP設(shè)計(jì)����、開發(fā)和組裝的專業(yè)技術(shù)使數(shù)據(jù)轉(zhuǎn)換系統(tǒng)的開發(fā)發(fā)生了巨大的變革��,實(shí)現(xiàn)了多任務(wù)應(yīng)用設(shè)計(jì)參數(shù)的最大靈活度(即組合和劃分)��。通過(guò)使用最先進(jìn)的技術(shù)(焊線��、倒裝芯片等)����,組合(或劃分)RF��、混合信號(hào)和數(shù)字處理半導(dǎo)體���,高級(jí)的SiP設(shè)計(jì)和組裝技術(shù)能為系統(tǒng)設(shè)計(jì)師帶來(lái)最高性能�����、最低成本的高頻數(shù)據(jù)轉(zhuǎn)換系統(tǒng)平臺(tái)����。

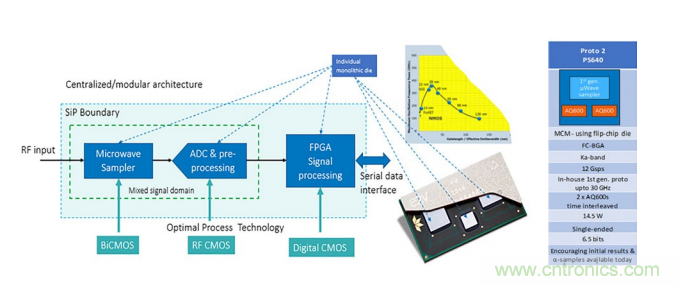

圖 6a

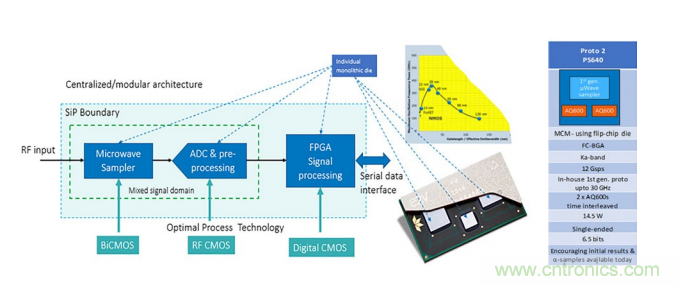

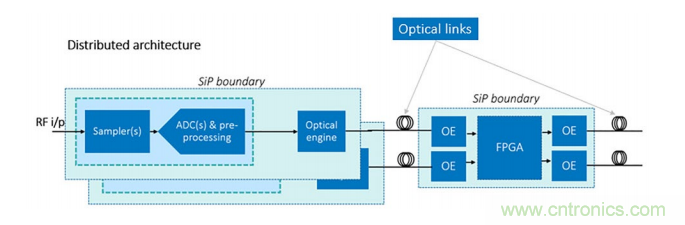

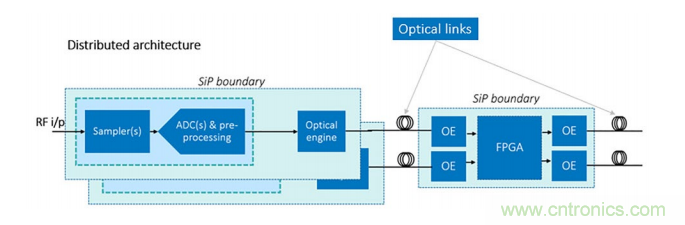

例如����,圖6的PS640是一款SiP實(shí)現(xiàn)的RF數(shù)據(jù)轉(zhuǎn)換系統(tǒng)產(chǎn)品,目前正在研發(fā),用于未來(lái)的L波段到Ka波段的頻率接收機(jī)(1GHz至40GHz)��。PS640使用Teledyne e2v基于STMicro BiCMOS055工藝設(shè)計(jì)的新型THA和兩片互相交織的EV12AQ600 ADC��,是一款“集中式”的高速SiP數(shù)據(jù)轉(zhuǎn)換接收器(Rx)�����。圖6也描述了其性能指標(biāo)�。圖7描述了一種相同的數(shù)據(jù)轉(zhuǎn)換系統(tǒng)的未來(lái)概念�����,這是一種“分布式”數(shù)據(jù)轉(zhuǎn)換接收器的實(shí)現(xiàn)方式�,使用光引擎(包含在SiP中)驅(qū)動(dòng)數(shù)字處理器(FPGA),實(shí)現(xiàn)最大軟件化(軟件中心)�����。

圖 6b

圖 7

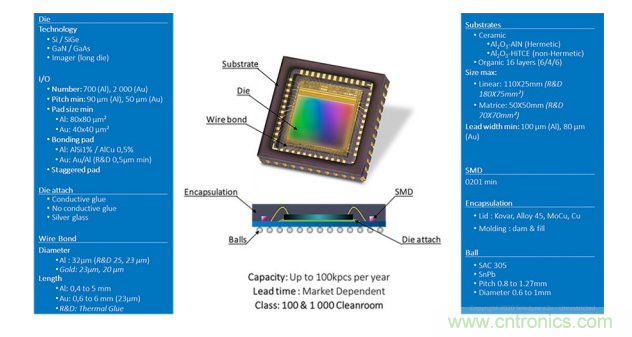

TE2V的高級(jí)SiP組裝技術(shù)

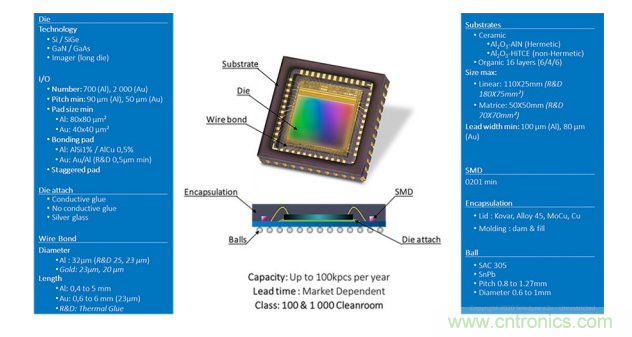

SiP是將多個(gè)器件(主動(dòng)器件或被動(dòng)器件)封裝在一起的單個(gè)設(shè)備��。SiP用于在電子系統(tǒng)層面執(zhí)行多項(xiàng)功能�����。嵌入在SiP中的半導(dǎo)體器件(包括被動(dòng)器件)可以水平和/或垂直堆疊在基材上,然后進(jìn)行封裝��。半導(dǎo)體可以通過(guò)焊線或焊接凸點(diǎn)的方式與基材連接(也可以用于將裸片堆疊成垂直的結(jié)構(gòu))�。如前所述,數(shù)據(jù)轉(zhuǎn)換SiP可能包含多個(gè)裸片���,如前置放大器�、混頻器���、ADC�����、DAC���,專用處理器、存儲(chǔ)集成電路和被動(dòng)器件(如電阻和電容)�����。這些裸片是使用不同的安裝技術(shù)固定在同一個(gè)基材上��。SiP的組裝技術(shù)促進(jìn)了細(xì)分市場(chǎng)的發(fā)展���,特別是與超高RF(地面和非地面)�、需要MEMs電路的物聯(lián)網(wǎng)(IOT)、移動(dòng)和可穿戴設(shè)備等應(yīng)用相關(guān)的領(lǐng)域�。憑借一系列的使用SiP技術(shù)的產(chǎn)品和封裝解決方案,Te2v為工業(yè)��、醫(yī)療����、航空、軍事����、科學(xué)和空間等應(yīng)用的細(xì)分市場(chǎng)提供設(shè)計(jì)和組裝服務(wù)�����。此外�����,Teledyne e2v的許多產(chǎn)品都是通過(guò)與NXP�����、Everspin、Micron等公司的戰(zhàn)略合作開發(fā)的�����。

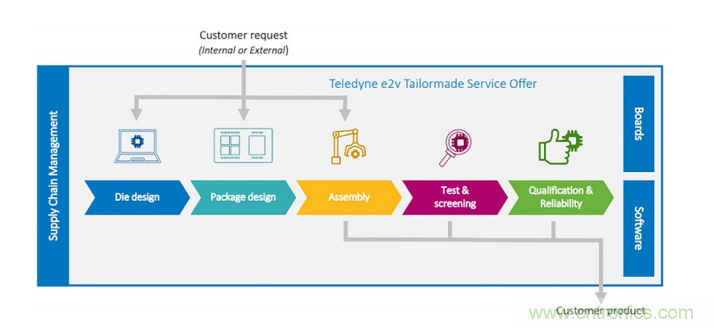

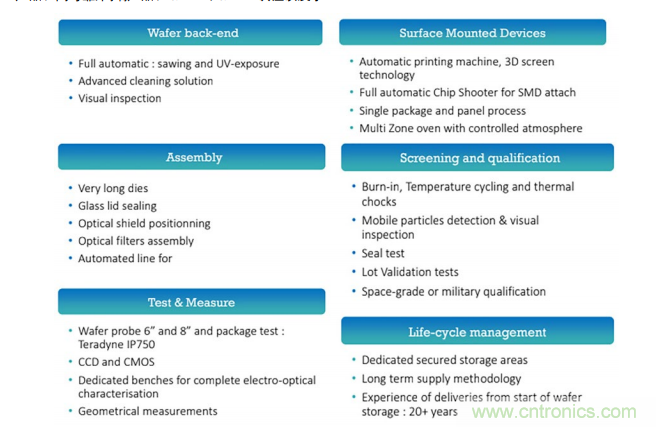

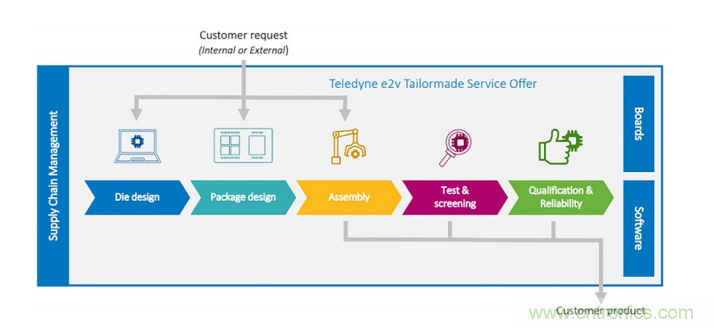

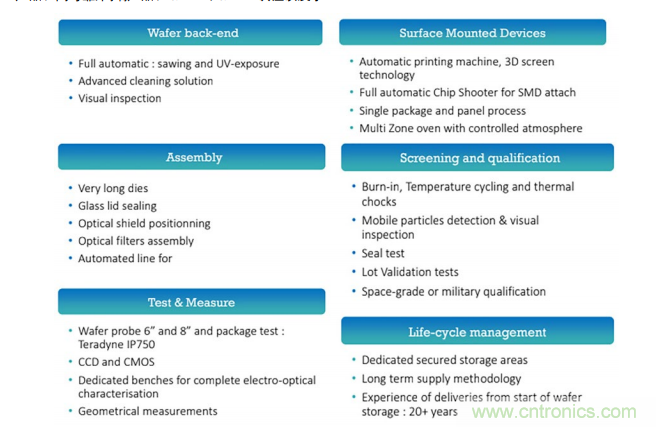

Te2v可提供一系列SiP設(shè)計(jì)開發(fā)的供應(yīng)鏈管理服務(wù)����,包括:裸片設(shè)計(jì)、封裝設(shè)計(jì)�、高可靠組裝、高性能速度測(cè)試�����、質(zhì)量服務(wù)和半導(dǎo)體生命周期管理(SLiMTM�����,見圖 8)����。Te2v擁有超過(guò)40年的宇航設(shè)計(jì)經(jīng)驗(yàn),包括ADC�、DAC、微處理器�����、存儲(chǔ)器以及內(nèi)部測(cè)試和質(zhì)量服務(wù),能為所有細(xì)分市場(chǎng)提供滿足任何質(zhì)量等級(jí)需求的高級(jí)SiP的產(chǎn)品和服務(wù)�����。Te2v的高級(jí)的SiP組裝技術(shù)包括:焊線��、倒裝芯片�����、有機(jī)和陶瓷封裝(密封和非密封)以及混合組裝��。

圖 8

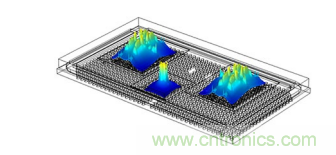

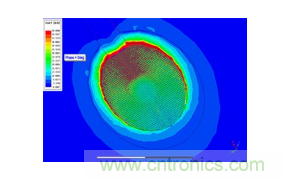

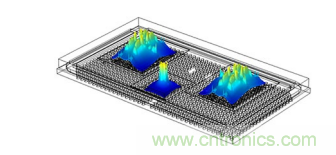

當(dāng)然��,在組裝之前��,高級(jí)高速SiP開發(fā)需要封裝仿真和封裝參數(shù)的測(cè)試��,以評(píng)估散熱和可靠性��。例如�����,圖9介紹了上文提到的PS640的熱仿真���。對(duì)于散熱設(shè)計(jì)��,將多個(gè)裸片緊密地放置在一起是一個(gè)挑戰(zhàn)���。為了準(zhǔn)確預(yù)測(cè)器件最關(guān)鍵區(qū)域的結(jié)溫,需要進(jìn)行仔細(xì)的熱仿真���。

圖 9 - PS640 SiP的熱仿真

Te2v使用與設(shè)計(jì)師和客戶討論商定的邊界條件���,使仿真的性能匹配最終的測(cè)試結(jié)果(這對(duì)于SiP集成的關(guān)鍵

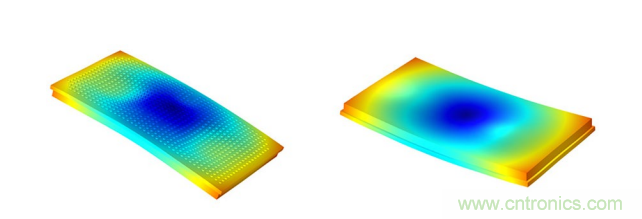

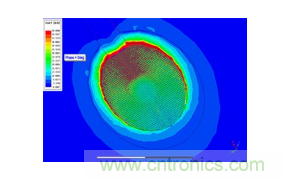

器件是必需的)。此外��,Te2v使用高頻3D場(chǎng)解算器(Ansys HFSS)對(duì)RF SiP的開發(fā)進(jìn)行仿真和設(shè)計(jì)��。HFSS是一款用于電磁結(jié)構(gòu)的商業(yè)有限元方法解算器����,適用于SiP封裝包含的復(fù)雜RF電子電路/半導(dǎo)體器件、濾波器��、傳輸線的封裝設(shè)計(jì)(見圖 10)�。

圖 10 - 對(duì) PS640 進(jìn)行 40GHz 模擬輸入的 3D 場(chǎng)解算器仿真 (Ansys HFSS) 顯示封裝到 THA 的裸片之間的連接狀況��,并分析了硅金屬填充里的信號(hào)傳遞�����。

在這個(gè)例子里��,Te2v的封裝團(tuán)隊(duì)和負(fù)責(zé)Te2v的SiP開發(fā)流程的半導(dǎo)體團(tuán)隊(duì)共同設(shè)計(jì)了這個(gè)RF模擬前端����。由于嵌入在單個(gè)有機(jī)基材里的硅技術(shù)有所不同���,以及C4(受控塌陷芯片連接 - 倒裝芯片凸點(diǎn))和C5(焊球)機(jī)電接口中的RoHS焊點(diǎn)����,SiP設(shè)計(jì)的可靠性是一個(gè)重大的工程挑戰(zhàn)�����。Te2v不斷開發(fā)新技術(shù)�����,通過(guò)熱機(jī)械分析�����,并考慮諸如焊料蠕變和粘塑性等的非線性行為�,快速并準(zhǔn)確地預(yù)測(cè)產(chǎn)品的翹曲和板級(jí)的可靠性

(見圖11)。

圖 11 - PS640 在室溫組裝后發(fā)生的封裝翹曲的 50 倍放大圖

具體的設(shè)計(jì)和組裝服務(wù)還包括:定制產(chǎn)品����、中/低用量產(chǎn)品、高可靠/高端產(chǎn)品���、QML-V/QML-Y認(rèn)證以及宇航認(rèn)證(參考圖12中的技術(shù)總結(jié)):

圖 12 - Te2v 的高級(jí)組裝技術(shù)�����,可用于 SIP 的組裝

圖 13 - Te2v 的高級(jí)焊線(上)和倒裝芯片(下)技術(shù)�,可用于 SIP 的組裝

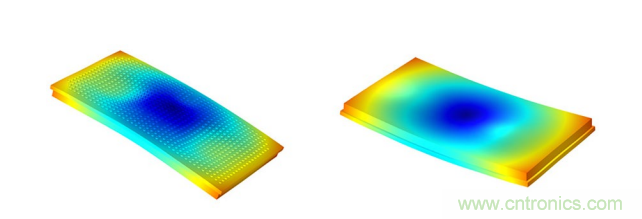

圖13說(shuō)明了Te2v的高級(jí)SiP焊線和倒裝芯片組裝技術(shù)�。對(duì)于焊線,圖13(上圖)說(shuō)明了滿足不同半導(dǎo)體類型(Si�����、GaN����、GaAs等)和封裝類型的最新發(fā)展所需的眾多組裝技術(shù)����。隨著新一代的半導(dǎo)體和封裝的發(fā)布����,必須開發(fā)新的焊線技術(shù),以滿足性能的要求��。焊線大約占所有電子封裝組裝(包含flash存儲(chǔ)器和傳感器等)的三分之二���。對(duì)于一些硅節(jié)點(diǎn)�����,如MEMS傳感器�,無(wú)法使用先進(jìn)的倒裝芯片互聯(lián)技術(shù)�。在這些情況下,焊線依然具有成本和可靠性方面的優(yōu)勢(shì)���。

倒裝芯片技術(shù)(也如圖13所示)基于半導(dǎo)體頂部形成的一系列凸起或銅柱��。倒裝芯片的流程和傳統(tǒng)IC的制造類似��,只需要增加幾個(gè)步驟��。在制造過(guò)程接近尾聲時(shí)��,對(duì)焊盤進(jìn)行金屬化或焊料預(yù)處理����,使其更容易焊接��。在最后的晶圓流程中��,焊接凸起會(huì)在晶圓頂部的

芯片焊盤上形成���,然后像往常一樣從晶圓上切下芯片�。為了將芯片安裝在外部電路(SiP電路板和/或另一個(gè)芯片或裸片)上����,需要翻轉(zhuǎn)芯片使其頂部朝下,并使它的焊盤與外部電路的焊盤對(duì)齊�,然后進(jìn)行回流焊(通常使用熱超聲焊接或回流焊接),以使它們互相連接���。這會(huì)在芯片電路和底部之間留下了一個(gè)很小的空間����。在很多情況下,需填充電氣絕緣的粘合劑�����,以保證更強(qiáng)的機(jī)械連接���,并產(chǎn)生熱橋��,確保焊點(diǎn)不會(huì)由于芯片和系統(tǒng)的其他部分的熱量不同而受到應(yīng)力�。這些填充物減少了芯片和板子之間的熱膨脹系數(shù)的不匹配帶來(lái)的影響����,防止應(yīng)力集中于焊點(diǎn),防止器件過(guò)早失效�。倒裝芯片技術(shù)與焊線技術(shù)不同,在焊線技術(shù)中����,芯片被簡(jiǎn)單地安裝,然后用線將芯片的焊盤和外部電路連接起來(lái)�����。

TE2V:為高級(jí)SiP的設(shè)計(jì)和組裝提供一站式服務(wù)

在性能生命周期內(nèi),SiP可降低特定產(chǎn)品和系統(tǒng)的總體成本�����,特別是與其他設(shè)計(jì)選項(xiàng)(如SoC等)相比時(shí)����。SiP可在產(chǎn)品生命周期的各個(gè)階段減少總體的系統(tǒng)開發(fā)成本���,如:

1. 降低工程成本:在工程開發(fā)時(shí)間�����、材料和上市時(shí)間方面顯著降低設(shè)計(jì)的難度����。

2. 降低PCB成本:簡(jiǎn)化特定器件的開發(fā)和使用(利用COTS或定制半導(dǎo)體)�。

3. 降低組裝成本:將多個(gè)器件集成到一個(gè)封裝里,可在系統(tǒng)整體制造流程中顯著降低成本��。

4. 降低供應(yīng)鏈成本:簡(jiǎn)化供應(yīng)鏈��。來(lái)自不同制造商的多個(gè)器件可被單個(gè)SiP取代�,這樣只需管理較少的供應(yīng)商和器件����,可大大簡(jiǎn)化供應(yīng)鏈����。

5. 驗(yàn)證:子系統(tǒng)和系統(tǒng)級(jí)的測(cè)試和認(rèn)證。

Te2v的高級(jí)SiP設(shè)計(jì)和組裝服務(wù)成為所有細(xì)分市場(chǎng)和產(chǎn)品類型的“一站式商店”(參見圖14)�。簡(jiǎn)單來(lái)說(shuō),Te2v不但為宇航級(jí)的應(yīng)用提供設(shè)計(jì)����、組裝和認(rèn)證服務(wù),也面向其他所有的細(xì)分市場(chǎng)����、應(yīng)用和質(zhì)量等級(jí)。

圖 14

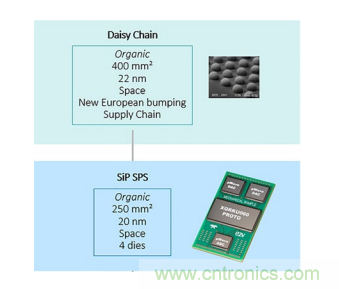

最后���,隨著高級(jí)系統(tǒng)的發(fā)展進(jìn)入下一個(gè)十年��,SiP技術(shù)已成為減少門長(zhǎng)度�、減小半導(dǎo)體尺寸的關(guān)鍵要素���。隨著越來(lái)越大的SoC逐漸成為SiP包含的眾多器件之一�����,使用有機(jī)基材和封裝材料進(jìn)行可靠組裝(焊線或倒裝芯片)的技術(shù)需要大量的技術(shù)投資�。當(dāng)前,Te2v正準(zhǔn)備在未來(lái)幾年內(nèi)實(shí)現(xiàn)這類技術(shù)的進(jìn)步�����,所有的技術(shù)研發(fā)都由ESA贊助�����。

結(jié)語(yǔ)

當(dāng)前�,數(shù)據(jù)轉(zhuǎn)換系統(tǒng)的設(shè)計(jì)師正在經(jīng)歷半導(dǎo)體工藝選擇(和幾何尺寸)�、電路小型化需求以及不斷增加的開發(fā)成本等關(guān)鍵設(shè)計(jì)參數(shù)的挑戰(zhàn)。此外����,高級(jí)系統(tǒng)的開發(fā)可以使用越來(lái)越先進(jìn)的ADC、DAC���、微處理器和存儲(chǔ)器件�����。在工業(yè)��、醫(yī)療�、航空電子、儀器儀表�����、通信��、軍事和宇航應(yīng)用領(lǐng)域�����,一個(gè)系統(tǒng)設(shè)計(jì)的問(wèn)題一直存在�����,即如何在模擬電路和數(shù)字電路之間取得平衡�����,以實(shí)現(xiàn)最大的軟件/系統(tǒng)靈活性(從傳感器到計(jì)算機(jī)輸入/輸出)?,F(xiàn)在,高級(jí)SiP(系統(tǒng)級(jí)封裝)技術(shù)的發(fā)展在所有的細(xì)分市場(chǎng)和應(yīng)用中推動(dòng)了數(shù)據(jù)轉(zhuǎn)換系統(tǒng)的設(shè)計(jì)從硬件中心到軟件中心的變革�����。Teledyne e2v的SiP設(shè)計(jì)、開發(fā)和組裝的專業(yè)技術(shù)革新了系統(tǒng)級(jí)設(shè)計(jì)�,實(shí)現(xiàn)了最大的靈活性和多任務(wù)的能力。Teledyne e2v擁有超過(guò)40年的RF��、混合信號(hào)和數(shù)字處理應(yīng)用的封裝設(shè)計(jì)經(jīng)驗(yàn)�����,其最先進(jìn)的SiP設(shè)計(jì)和組裝技術(shù)(焊線���、倒裝芯片、有機(jī)封裝等)將幫助系統(tǒng)設(shè)計(jì)師實(shí)現(xiàn)高頻直接RF數(shù)據(jù)轉(zhuǎn)換系統(tǒng)平臺(tái)的最高性能和最大價(jià)值���。

(來(lái)源:Teledyne e2v)