【導讀】圖1所示的這個電路提供一個同步寬頻帶發(fā)射器,可支持高達1150 MHz的超寬I/Q帶寬。該設計證明了高帶內信號性能,如高無雜散動態(tài)范圍(SFDR)、低誤差矢量幅度(EVM)和寬頻帶范圍內的平坦頻率響應。

電路功能與優(yōu)勢

圖1所示的這個電路提供一個同步寬頻帶發(fā)射器,可支持高達1150 MHz的超寬I/Q帶寬。該設計證明了高帶內信號性能,如高無雜散動態(tài)范圍(SFDR)、低誤差矢量幅度(EVM)和寬頻帶范圍內的平坦頻率響應。

多個通道間的同步性能對于象限誤差校正(QEC)尤為重要。啟用多芯片同步時,轉換器之間的延遲失配可能在一個時鐘周期內,并且存在對齊良好的同步時鐘。

高速同步的挑戰(zhàn)是要在過程、電壓和溫度(PVT)中達到數(shù)模(DAC)時鐘周期的精度。要達到這種精度,需要在DAC上實施同步邏輯塊,并且必須在板上精心設計布局和時鐘方案以與同步邏輯塊配合使用。

該電路可用于支持E頻段中的寬帶點對點應用,這可同時確保零中頻(ZIF)和復中頻(CIF)。出色的同步性能使其能夠支持雷達等應用中的嚴格對齊要求。

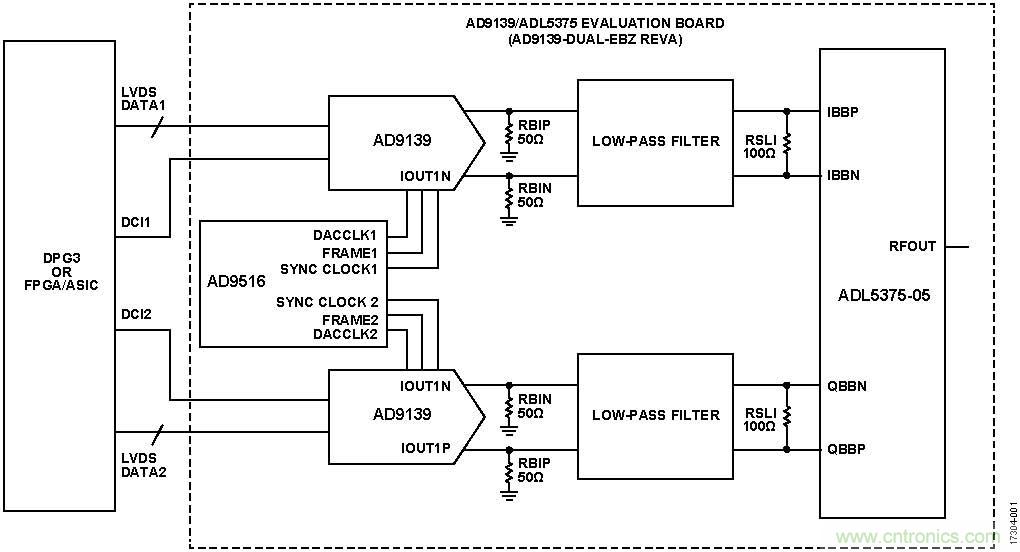

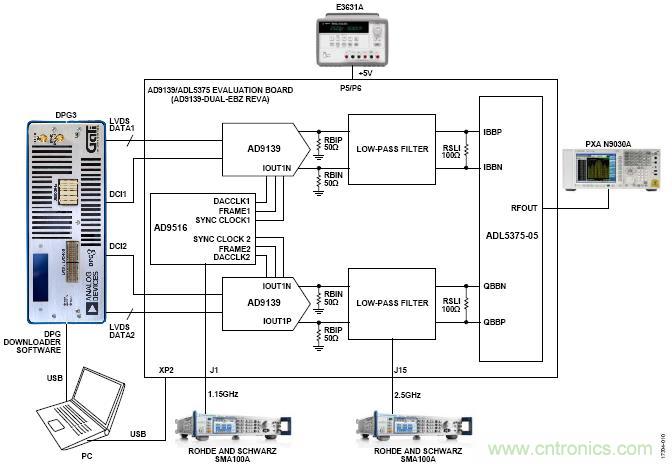

圖1.AD9139-DUAL-EBZ評估板功能框圖

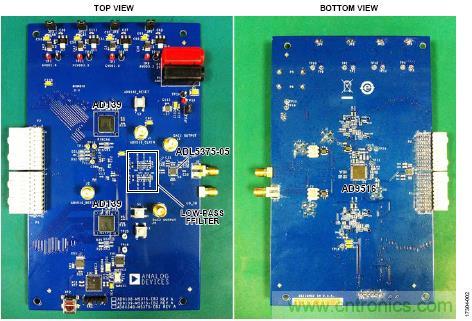

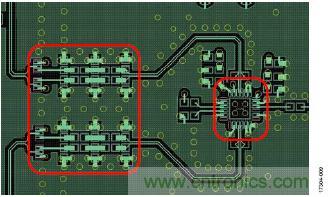

圖2.用于實現(xiàn)電路的AD9139-DUAL-EBZ評估板

電路描述

圖2所示的電路板使用雙AD9139單通道TxDAC、ADL5375-05寬帶正交調制器和AD9516-1時鐘發(fā)生器。

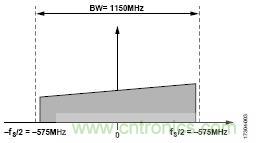

AD9139的數(shù)據(jù)時鐘輸入(DCI)頻率可高達575 MHz。由于在上升沿和下降沿捕獲的數(shù)據(jù)均饋入單個DAC,1×模式下的數(shù)據(jù)速率可高達1150 MSPS。為支持正交數(shù)據(jù),使用了兩個AD9139器件來生成基帶數(shù)據(jù)。每個通道的模擬輸出分別進入自己的低通濾波器。因此,參考設計可支持高達1150 MHz的復合帶寬,如圖3所示。在如此大范圍中的平坦度至關重要。由于AD9139包括一個可抵消DAC的內在sinc滾降影響的反sinc濾波器,DAC后的濾波器平坦度變得對總平坦度至關重要。對于并行低電壓差分信號(LVDS)接口,575 MHz的DDR時鐘頻率很高。需要仔細設計LVDS接口的時序。

圖3.雙AD9139器件的最大帶寬

正交調制器

ADL5375-05是一款寬帶正交調制器,輸出頻率范圍為400 MHz至6 GHz。ADL5375-05作為I/Q調制器與AD9139接口,該調制器的頻率范圍很寬,為400 MHz至6 GHz。AD9139的輸出和ADL5375-05的輸入共用0.5 V的相同共模電平。

時鐘產生和考慮事項

考慮到同步要求,兩個AD9139器件的DACCLK、同步時鐘和幀時鐘都必須對齊良好。AD9516-1支持必需的時鐘分配功能,以及為產生更高頻率而集成的壓控振蕩器(VCO)和鎖相環(huán)(PLL)。禁用VCO和PLL,并且AD9516-1處于時鐘分配模式時,更好的時鐘相位噪聲更利于高速對齊。作為時鐘分配模式使用時,在1 GHz輸出,分頻比為1,10 MHz頻偏處,加性相位噪聲為147 dBc/Hz。Rohde & Schwartz SMA100A具有出色的相位噪聲性能,用其作為AD9516-1的輸入時,AD9516-1的輸出總相位噪聲接近時鐘分配模式下AD9516-1的最小限值。

AD9139的多芯片同步

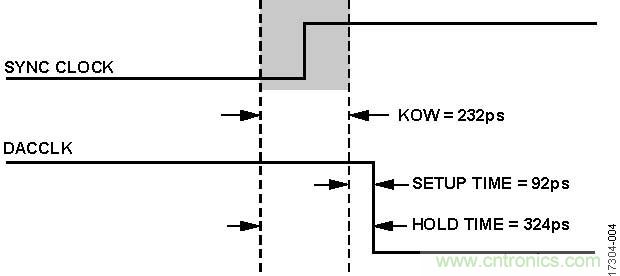

雙通道間的同步對于QEC至關重要。DACCLK和同步時鐘之間需要布局對稱。此外,DACCLK和同步時鐘之間的相位不得落在建立和保持時間窗口內(也稱為保持在窗口外(KOW))。

同步機制可以達到在DAC輸出上多個通道之間在PVT中的失配小于一個DAC時鐘周期。以下是實現(xiàn)測試性能的指南:

1.DACCLK 1和DACCLK 2必須在AD9139的引腳上對齊良好。DACCLK 1和DACCLK 2之間的不匹配將添加到輸出上的最終不匹配中。

2.同步時鐘1和同步時鐘2必須對齊良好,并且分別由DACCLK1和DACCLK2采樣,用作參考。

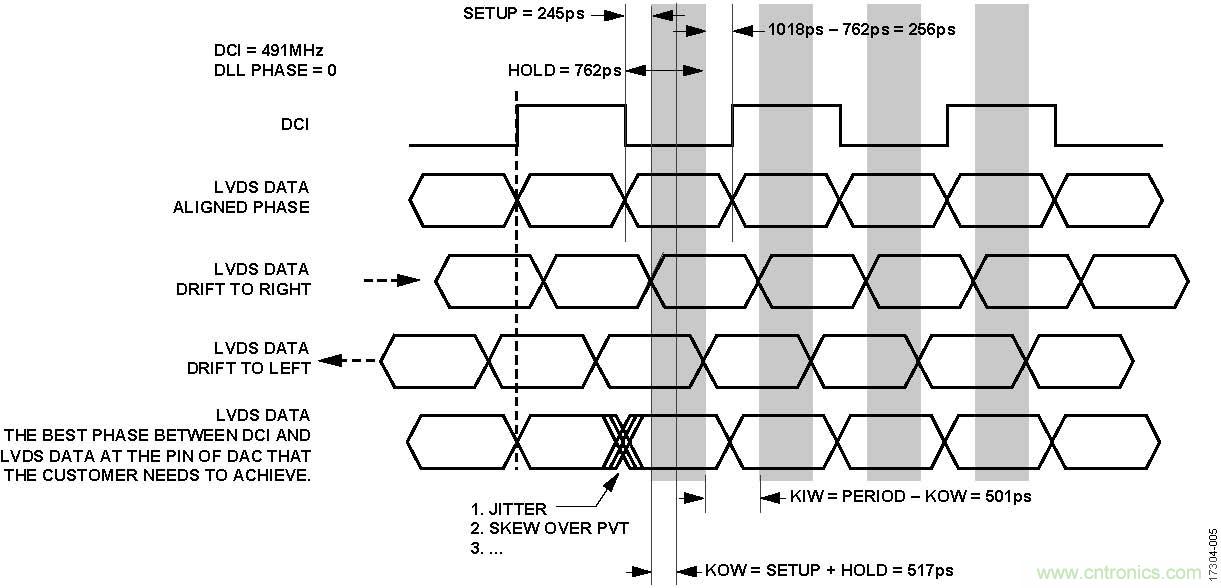

3.DACCLK和同步時鐘之間的相對相位不得落在KOW內,如圖4所示。

圖4.DACCLK和同步時鐘之間的時序要求

LVDS接口設計

DCI = 575 MHz時,在PVT中設計LVDS接口通常是一個挑戰(zhàn)。本節(jié)用一個例子說明如何設計和優(yōu)化該接口。

以圖5為例,DCI = 491 MHz。根據(jù)AD9139數(shù)據(jù)手冊規(guī)格,如果DCI和DATA的邊緣在AD9139的引腳上對齊良好,當延遲鎖相環(huán)(DLL)相位設置為零時,KOW(設置時間 + 保持時間)可置于有效窗口中間。

數(shù)據(jù)有效裕量由如下公式定義。

TDATA VALID MARGIN = TDATA PERIOD − TDATA SKEW − TDATA JITTER − (THOLD + TSETUP)

在整個過程變化、電壓和溫度中,TDATA VALID MARGIN必須> 0以確保數(shù)據(jù)的正確采樣。

When DCI = 491 MHz (see Figure 5),

DCI = 491 MHz(見圖5)時,

•TDATA PERIOD = 1018 ps

•THOLD + TSETUP = 517 ps

•TDATA SKEW + TDATA JITTER在PVT中必須小于501 ps,這是用戶實施的要求。TDATA SKEW包括LVDS數(shù)據(jù)總線延遲失配、PVT中DCI和DATA總線之間的偏斜等。

要優(yōu)化接口設計,用戶可執(zhí)行以下操作:

•在印刷電路板(PCB)上用盡可能短的相同長度的走線。

•通過確保以下各項,優(yōu)化現(xiàn)場可編程門陣列(PFGA):

○ DCI和DATA的邊緣在AD9139的引腳上對齊良好。

○ 在溫度和電壓變化時,DCI和DATA之間的漂移越小越好。

○ DCI和DATA之間的抖動越小越好。

掃描DLL相位后,AD9139的樣本錯誤檢測(SED)功能也可用于檢查DCI和DATA之間的時序關系。

圖5.LVDS時序要求

低通濾波器設計

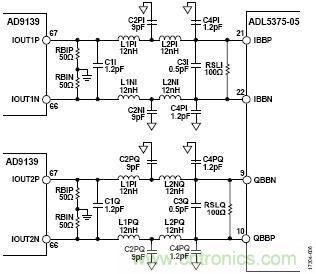

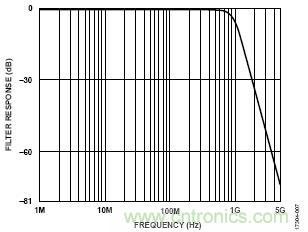

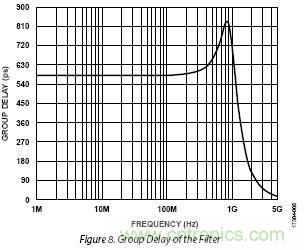

出于實驗目的,為了使AD9139的性能不被濾波器限制,在板上設計了一個在240MHz內具有良好平坦度和群延遲性能的濾波器。在實際產品開發(fā)中,可以通過增加濾波器的階數(shù)來增強帶外抑制。

圖6所示的濾波器拓撲結構是一個五階巴特沃茲濾波器,轉折頻率為900 MHz。此濾波器的仿真響應曲線如圖7所示。仿真平坦度為±0.1 dB(直流至240 MHz)。此濾波器的仿真群延遲曲線如圖7所示。

圖6.推薦的DAC調制器接口拓撲(FC = 900 MHz,五階巴特沃茲濾波器)

圖7.DAC調制器與900 MHz五階巴特沃茲濾波器接口的頻率響應(模擬)

圖8.濾波器的群延遲

布局建議

應特別注意AD9139和ADL5375接口的布局。以下是一些獲得較好噪聲和雜散性能的建議。圖9顯示了一個遵循這些建議的頂層布局圖:

?

● 將DAC、濾波器和調制器放在PCB的同一側。

● 收緊濾波器布局:減少L和C的禁區(qū)裕量。

● 將對地電容分三路接到GND平面。

● 縮短DAC到調制器的距離。

● 使所有I/Q差分走線長度保持良好的匹配。

● 濾波器端接電阻盡可能靠近調制器輸入端放置。

● DAC輸出50 Ω電阻盡可能靠近DAC放置。

● L和C使用0402封裝。

● 加寬經(jīng)過濾波器網(wǎng)絡的走線以降低信號損耗。

● 在所有DAC輸出走線、濾波器網(wǎng)絡、調制器輸出走線和LO輸入走線周圍設置通孔。

● 將本振(LO)和調制器輸出走線布設在不同的層上或彼此成90°角,防止耦合。

圖9.一般布局建議

訪問www.analog.com/CN0432-DesignSupport獲取設計支持包,在隨附的AD9139-DUAL-EBZ布局文件中了解有關正確布局的更多信息。

電路評估與測試

下節(jié)描述如何設置和測試評估板。這些步驟概述了實現(xiàn)評估板功能和結果所需的基本步驟。有關更詳細的信息,請參閱AD9139-DUAL-EBZ評估板快速入門指南。

需要的設備

需要使用以下硬件:

● AD9139-DUAL-EBZ

● AD-DPG3

● Agilent E3631A電源(或同等電源)

● 頻譜分析儀PXA N9030A

● Rohde & Schwartz SMA100A信號發(fā)生器

● 帶USB端口的PC

● USB電纜

需要使用以下軟件:

● DPG downloader

● ACE軟件

測試設置

下節(jié)描述使用64 QAM數(shù)字調制測量鄰道功率(ACP)和調制誤差率(MER)性能的詳細信息。測試設置靈活,也可以執(zhí)行其它測量。測試設置如下圖10所示。AD9139-DUAL-EBZ評估板的硬件、SPI軟件、快速入門指南(QSG)以及DPG3硬件和軟件均已發(fā)布。

使用一個Keysight E3631為P5/P6上的電路板提供5 V電源。使用一個R&S SMA100A為板上的AD9516-1提供輸入時鐘。再使用一個R&S SMA100A為ADL5375-05提供LO時鐘。AD9139通過串行外設接口(SPI)軟件進行編程。PC上運行的DPGDownloader生成AD9139的發(fā)射矢量并將其下載至DPG3。ADL5375-05的輸出饋入Keysight PXA N9030A。

圖10.測試設置功能框圖

測量結果

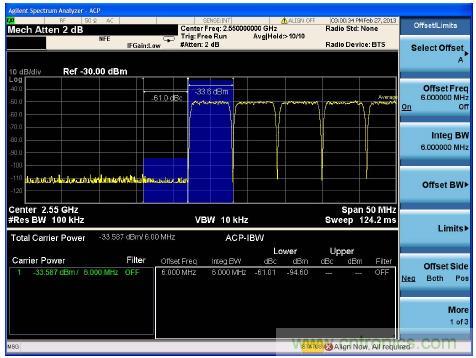

圖11.ACP測量,LO = 2.5 G,BW = 6 × 80 = 480 MHz (CIF)

圖12.MER/EVM測量,LO = 2.5 G,BW = 6 × 80 = 480 MHz (CIF)

推薦閱讀: