【導(dǎo)讀】作為一種復(fù)雜的集成電路,F(xiàn)PGA系統(tǒng)供電的電源的設(shè)計(jì)與一般的電子系統(tǒng)相比,要求也更高,需要具備高精度、高密度、可控性、高效及小型化等的特點(diǎn)。本文系統(tǒng)介紹了FPGA電源的不同特性,同時(shí)會(huì)通過實(shí)例,讓工程師更深入地了解各特性的意義,以及FPGA規(guī)范約束及其對(duì)電源設(shè)計(jì)的影響,以便快速完成FPGA系統(tǒng)的電源設(shè)計(jì)。

前言

FPGA (Field Programmable Gate Arrays) 是現(xiàn)今最復(fù)雜的集成電路之一。它們采用先進(jìn)的晶體管技術(shù)和芯片架構(gòu)實(shí)現(xiàn)高性能、小體積的高端產(chǎn)品,而為FPGA系統(tǒng)供電的電源與一般的電子系統(tǒng)相比,要求更高。

隨著市場(chǎng)上對(duì)FPGA系統(tǒng)應(yīng)用的普及,對(duì)其電源解決方案的需求也越來越旺盛,F(xiàn)PGA電源系統(tǒng)除了需要滿足基本要求外,還需要具備高精度、高密度、可控性、高效及小型化等的特點(diǎn)。

現(xiàn)實(shí)中,工程師希望將大部分時(shí)間花在編程上,而不想花太多的時(shí)間和精力考慮如何設(shè)計(jì)合適的電源耗材。所以在本文中,我們會(huì)介紹FPGA電源的不同特性,同時(shí)會(huì)通過實(shí)例,讓工程師更深入地了解各特性的意義,以及FPGA規(guī)范約束及其對(duì)電源設(shè)計(jì)的影響。

電壓精度

內(nèi)核電源電壓 (Core Power Supply) 是平衡FPGA功耗和性能的最重要關(guān)鍵要素之一。規(guī)格書中一般會(huì)列出可接受的電壓范圍,但此范圍并不是完整的描述,對(duì)FPGA而言,電源電壓在滿足線路運(yùn)作要求的同時(shí),也需要權(quán)衡和優(yōu)化。下圖一是以Intel的Arria 10 FPGA內(nèi)核電壓要求為例,其也代表了其他FPGA內(nèi)核的電壓要求。一般會(huì)顯示容差范圍額定電壓,例如Arria 10 FPGA為±0.03V,F(xiàn)PGA會(huì)在這個(gè)電壓窗口內(nèi)運(yùn)行得很好,但實(shí)際情況比圖片顯示復(fù)雜很多。

事實(shí)上,F(xiàn)PGA可以在不同電壓下工作,這具體取決于其特殊的制造公差以及所采用的特定邏輯設(shè)計(jì)。即使是同一電壓要求,一個(gè)FPGA所需的靜態(tài)電壓也可能是與另一個(gè)FPGA不同,所以在電源設(shè)計(jì)時(shí)必須要考慮對(duì)應(yīng)FPGA的動(dòng)態(tài)與靜態(tài)之間的變化而自行調(diào)控。

圖1:Arria 10 FPGA內(nèi)核電壓要求 (來源: Intel®Arria® 10 器件數(shù)據(jù)表)

動(dòng)態(tài)功率和靜態(tài)功率

設(shè)計(jì)合適的FPGA電源方案,目標(biāo)是產(chǎn)生恰當(dāng)?shù)男阅芩絹聿僮骶幊坦δ?,減少不必要的功耗。我們從半導(dǎo)體物理學(xué)的角度看,動(dòng)態(tài)和靜態(tài)功率都隨著內(nèi)核VDD的增加而顯著增加,因此我們的目標(biāo)是讓FPGA有足夠電壓來正常運(yùn)行,以滿足其時(shí)間要求——因?yàn)檫^量功耗不但對(duì)提高性能沒有任何幫助,相反它會(huì)令晶體管漏電流隨著溫度的升溫,消耗更多的不必要的電力。由于這些原因,當(dāng)務(wù)之急是優(yōu)化設(shè)計(jì)和工作點(diǎn)的電壓。

該優(yōu)化過程需要非常精確的電源才能獲得成功。如果內(nèi)核電壓低于要求,則FPGA可能由于時(shí)序錯(cuò)誤而發(fā)生故障。如果內(nèi)核電壓漂移超過最大規(guī)格,可能會(huì)損壞FPGA,或者可能會(huì)在邏輯中產(chǎn)生保持時(shí)間故障。所以,必須考慮電源容差范圍來防止所有這些情況,并且僅保證保持在規(guī)格限制內(nèi)的指令電壓。

問題是大多數(shù)電源調(diào)節(jié)器都不夠準(zhǔn)確。調(diào)節(jié)電壓可以在被指令電壓附近的公差范圍內(nèi)的任何地方,并且它可以隨負(fù)載條件、溫度和老化而漂移。±2%容差的電源即表示可以在4%的電壓范圍內(nèi)輸出任何值。為了補(bǔ)償電壓處于2%過低的可能性,被指令電壓必須比滿足時(shí)序所需的電壓提高2%。如果經(jīng)過調(diào)節(jié)器后電壓漂移到高于被指令電壓2%處,它將比該工作點(diǎn)所需的最小電壓運(yùn)行高4%。這仍然符合規(guī)定的FPGA所需的電壓要求,卻浪費(fèi)了大量功率,如下圖2所示。

圖2:電源調(diào)節(jié)器容差權(quán)衡

解決這一問題的方案是選擇能夠以更嚴(yán)格的電壓容差運(yùn)行的電源調(diào)節(jié)器。使用具有±0.5%容差的調(diào)節(jié)器,可以在所需的工作頻率下、更接近所需的最小規(guī)格內(nèi)工作,并且保證與所需的電壓相差小于1%。這樣,好讓FPGA在最小功耗的情況下,正常工作。

高電量需求

FPGA系統(tǒng)中的器件通常需要不同調(diào)節(jié)電壓,例如電壓的內(nèi)核電壓處理器,其要求電壓可以是0.8V、1.0V、1.2V、1.5V或1.8V等。雖然是低電壓供應(yīng),但其密集的晶體管結(jié)構(gòu)及長(zhǎng)期保持高速運(yùn)作的情況下,供電電源方案可能需要10A或以上,具體的處理器要求通常決定了其他電源要求,例如負(fù)載瞬態(tài)恢復(fù)、待機(jī)模式等,這需要負(fù)載點(diǎn)(Point-of-Load,或簡(jiǎn)稱PoL)穩(wěn)壓電源專為核心電壓設(shè)計(jì)。 PoL穩(wěn)壓電源是一種高性能穩(wěn)壓器,其各Vout電壓軌獨(dú)立于各自的負(fù)載設(shè)置。這有助于解決高瞬態(tài)電流的要求以及諸如FPGA高性能半導(dǎo)體器件的低噪聲要求。例如ADI 公司的LTM4678系列,包含兩組能夠同時(shí)提供高密度的電源供應(yīng)輸出,分別為1V@25A 及1.8V@25V。

圖3:ADI的LTM4678應(yīng)用線路圖

可控性需求

FPGA中含有大量而復(fù)雜編排的晶體管,一塊芯片包含數(shù)億個(gè)晶體管,當(dāng)中被分割成可以設(shè)計(jì)并獨(dú)立管理的內(nèi)核段、模塊段和隔斷。這些特定的編排是的其具有許多不同電源域,在電壓、電流、紋波和噪聲以外,還包括啟動(dòng)、關(guān)斷和故障條件期間的序列順序,故可控性的FPGA電源需要妥善管理輸出的次序及其電量。

市場(chǎng)中較新的FPGA在規(guī)格中會(huì)提供針對(duì)啟動(dòng)和關(guān)斷電源時(shí)的序列順序提出特定的要求,確保FPGA正常開啟及復(fù)位,保持最小的電流消耗,并在電源轉(zhuǎn)換期間將I/O保持在正確的三態(tài)配置下。再以Arria 10為例,其技術(shù)規(guī)格將電源分為三個(gè)序列組(1、2、3),并要求它們按升序排列為1、2、3,然后按相反的順序降序排列:3、 2、1。

圖4:Arria 10電源組順序示意圖

例如ADI公司的LTC2936可以提供六個(gè)可編程閾值模擬比較器,用于檢測(cè)快速事件并將數(shù)字狀態(tài)發(fā)送到邏輯。該器件還有三個(gè)可編程GPIO引腳,可提供額外的功能。該可編程IC包括EEPROM,后者可在啟動(dòng)時(shí)近乎即時(shí)地工作;該IC還能通過其I2C/SMBus接口存儲(chǔ)故障遙測(cè)數(shù)據(jù)以便進(jìn)行調(diào)試。

圖5:ADI的LTC2936應(yīng)用方框圖

FPGA 開發(fā)套件支持

工程師可利用FPGA開發(fā)套件協(xié)助開發(fā)。例如Arria 10 SoC開發(fā)套件 (DK-SOC-10AS066S-A)展示了用于Arria 10 SoC 電源要求的ADI的LTM4677µmodule電源解決方案。

在套件中,內(nèi)核電源的工作電壓為0.95V,工作電流為30A。由于這些電源要求相對(duì)寬松,單個(gè)LTM4677模塊就可輕松提供所需電流(最高36A)。對(duì)于要求更多電流且條件更為苛刻的應(yīng)用,最多可以并行運(yùn)行四個(gè)LTM4677模塊,以提供高達(dá)144A的電流,如圖7所示。

圖6:Arria10 SoC開發(fā)套件

圖7:利用四個(gè)LTM4677模塊并聯(lián)的應(yīng)用電路圖,可提供高達(dá)144A的電流

利用參數(shù)列表選料

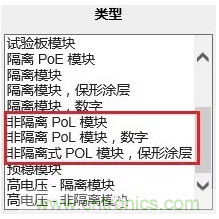

了解應(yīng)用的要求之后,工程師可在Digi-Key官網(wǎng)上,在「電源 - 板安裝」分類中,選擇「直流轉(zhuǎn)換器」子分類。「應(yīng)用篩選程序」中,工程師可在「類型」中找到「POL」,或直接在「在結(jié)果中搜尋」中輸入「POL」以篩選PoL穩(wěn)壓電源。

圖8

結(jié) 語(yǔ)

在FPGA系統(tǒng)中,電源解決方案是工程師需要考慮的重要題目之一。與一般的電腦要求不同,F(xiàn)PGA電源需要高精度、可編程功能、可調(diào)度等要素,及最重要的「高能量密度」,即低電壓/高電流。業(yè)界已將這類型的產(chǎn)品研發(fā)歸類于負(fù)載點(diǎn)(PoL)穩(wěn)壓電源。

為方便工程師選料,Digi-Key官網(wǎng)上的「電源 - 板安裝」分類中的「直流轉(zhuǎn)換器」子分類中,在「類型」中已將PoL產(chǎn)品列出,方便工程師更快更準(zhǔn)確地選料。

來源:得捷電子DigiKey

作者:Kevin Chow