【導(dǎo)讀】過去,任意波形發(fā)生器最棘手的部分是輸出級(jí)的設(shè)計(jì)。典型信號(hào)發(fā)生器的輸出范圍在25 mV 到5 V 之間。為了驅(qū)動(dòng)一個(gè)50 Ω 的負(fù)載,傳統(tǒng)設(shè)計(jì)采用高性能分立式器件,并聯(lián)大量集成器件,或者成本昂貴的ASIC,而要構(gòu)造出穩(wěn)定且可編程范圍較寬的高性能輸出級(jí),設(shè)計(jì)師往往要投入無數(shù)小時(shí)的時(shí)間?,F(xiàn)在,技術(shù)進(jìn)步帶來的放大器可以驅(qū)動(dòng)這些負(fù)載,降低輸出級(jí)的復(fù)雜性,同時(shí)還能減少成本、縮短上市時(shí)間。

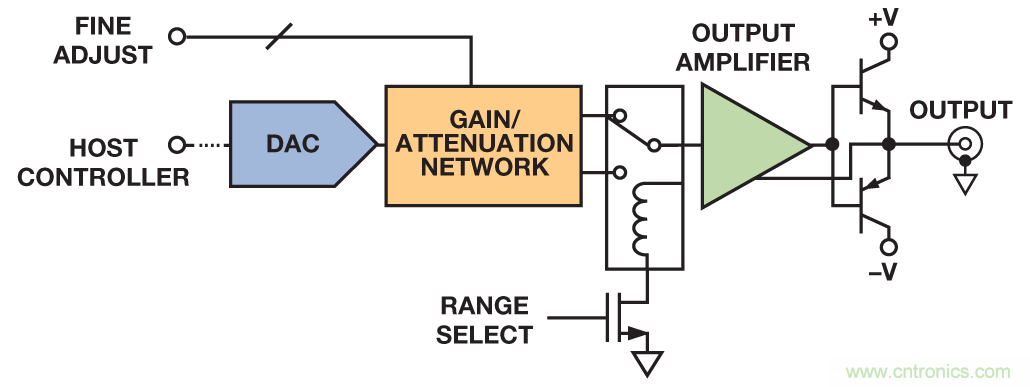

圖1. 典型信號(hào)發(fā)生器模型

在使用通用信號(hào)發(fā)生器時(shí),先輸入一個(gè)頻率,然后按下一個(gè)按鈕,最后儀器產(chǎn)生一個(gè)新的頻率。接下來,輸入所需輸出功率,再按下另一個(gè)按鈕。在切換內(nèi)部網(wǎng)絡(luò)、調(diào)整輸出電平時(shí),繼電器發(fā)出咔噠聲。這種非連續(xù)運(yùn)行模式是補(bǔ)償寬可編程范圍缺失問題的必要條件。本文提出一種新的架構(gòu),它可以解決輸出級(jí)設(shè)計(jì)中的一半問題。

克服這個(gè)前端設(shè)計(jì)挑戰(zhàn)的兩個(gè)關(guān)鍵組件是:提供高速、高電壓和高輸出電流的高性能輸出級(jí);以及帶連續(xù)線性dB 調(diào)諧的可變增益放大器(VGA)。這種設(shè)計(jì)以20MHz 的性能為目標(biāo),幅度為22.4 V(+39 dBm),負(fù)載為50 Ω。

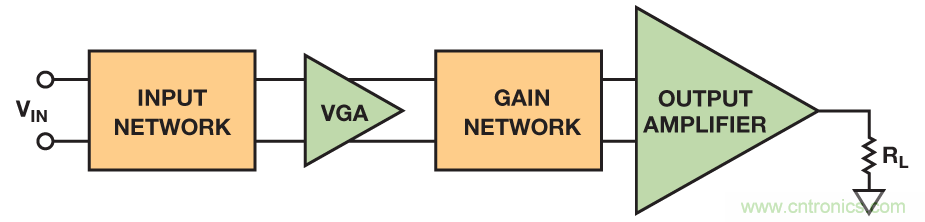

圖2. 更小、更簡單的信號(hào)發(fā)生器輸出級(jí)

新型緊湊式輸出級(jí)

初始信號(hào)可能來自數(shù)模轉(zhuǎn)換器(DAC)以產(chǎn)生復(fù)雜波形,也可能來自直接數(shù)字頻率合成(DDS)器件以產(chǎn)生正弦波。任一情況下,其規(guī)格和功率調(diào)整能力都可能達(dá)不到理想狀態(tài)。第一個(gè)要求是用VGA提供衰減或增益。但許多VGA 提供的增益是有限的,往往不足以在本應(yīng)用中發(fā)揮作用。

如果VGA 的輸出可以設(shè)為目標(biāo)電平,則無論輸入為何,都可以強(qiáng)制輸出已知幅度。例如,如果所需輸出幅度為2 V,且功率輸出級(jí)的增益為10,則VGA 的輸出幅度應(yīng)調(diào)節(jié)至0.2 V。當(dāng)輸出級(jí)設(shè)計(jì)正確時(shí),輸出幅度最終由VGA 輸出設(shè)定。不幸的是,多數(shù)VGA因可編程范圍有限而成了瓶頸問題。

AD8330是實(shí)現(xiàn)50 dB 范圍的首款VGA,但AD8338則樹立了新的標(biāo)桿,這款新型低功耗VGA 擁有高達(dá)80 dB 的可編程范圍。典型的高品質(zhì)信號(hào)發(fā)生器的輸出幅度范圍為25 mV 至5 V。高達(dá)46 dB的可調(diào)范圍超過了市面上多數(shù)現(xiàn)有VGA 的能力范圍。理想條件下,經(jīng)典信號(hào)發(fā)生器的輸出幅度可能為0.5 mV 至5 V,無需使用繼電器或開關(guān)網(wǎng)絡(luò)。滿量程連續(xù)可調(diào),不存在開關(guān)和繼電器的非連續(xù)性問題。另外,不用繼電器還可以延長儀器壽命,提高系統(tǒng)可靠性。

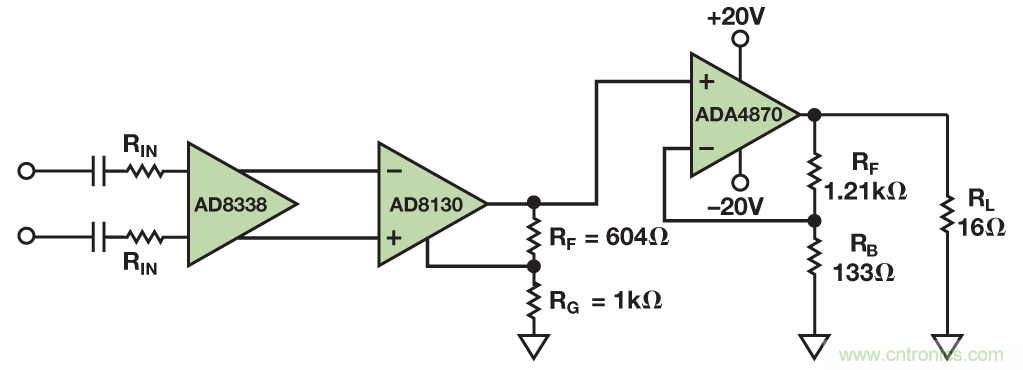

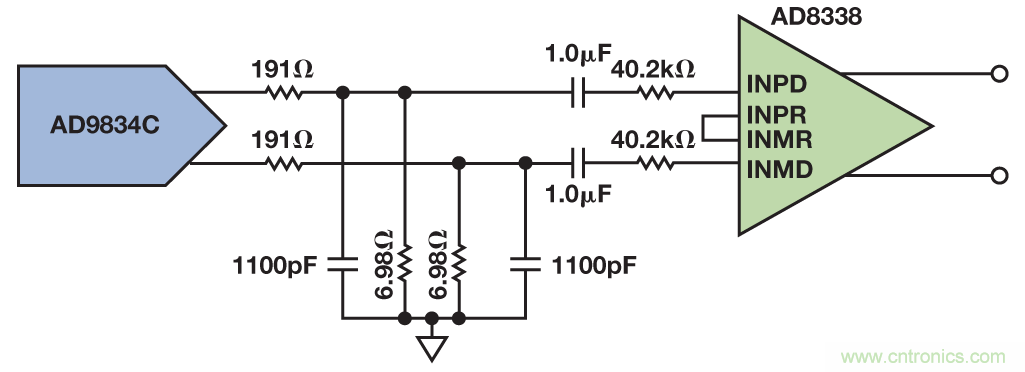

現(xiàn)代DAC 和DDS 器件一般搭載差分輸出,要求設(shè)計(jì)師使用一個(gè)變壓器,用單端連接損失一半信號(hào),或者添加一個(gè)差分轉(zhuǎn)單端轉(zhuǎn)換器。AD8338 具有天然的適用性,提供全差分接口,如圖3 所示。對于正弦波應(yīng)用,用DDS 取代DAC。

圖3. 把DAC 連接至AD8338 的網(wǎng)絡(luò)示例

AD8338 的一個(gè)主要特點(diǎn)是靈活的輸入級(jí)。作為一款輸入VGA,它通過ADI 研究員Barrie Gilbert 發(fā)明的"H-amp"拓?fù)浣Y(jié)構(gòu)來控制輸入電流。該設(shè)計(jì)用反饋來平衡輸入電流,同時(shí)使內(nèi)部節(jié)點(diǎn)電壓維持于1.5 V。正常條件下,使用500 Ω 輸入電阻,最大1.5 V輸入信號(hào)會(huì)產(chǎn)生3 mA 的電流。如果輸入幅度較大,比如15 V,則將一個(gè)較大的電阻連接至"直接"輸入引腳。該電阻的大小必須合適,以得到相同的3 mA 電流:

單端15 V 信號(hào)將以差分方式輸出1.141 V。此時(shí),最小增益條件下,AD8338 提供28.4 dB 衰減,因此,最大可能增益為+51.6 dB。作為一種低功耗器件,在1 kΩ 負(fù)載條件下,典型輸出擺幅為1.5 V。

輸入VGA 的功率必須滿足以下條件:其總增益范圍在不同設(shè)定點(diǎn)周圍。首先,確定信號(hào)發(fā)生器產(chǎn)生最大輸出需要的輸出電平。許多商用發(fā)生器為50 Ω 負(fù)載(正弦波)只提供250 mW rms (+24 dBm)的最大輸出功率。這無法滿足需要更多輸出功率的應(yīng)用需求,比如測試高輸出高頻放大器、超聲脈沖發(fā)生等。

電流反饋放大器(CFA)技術(shù)的進(jìn)步意味著,這不再是個(gè)問題。ADA4870CFA 可以用±20 V 電源驅(qū)動(dòng)1 A(17 V)。對于正弦波,可以在滿負(fù)載條件下輸出最高23 MHz 的頻率,使其成為新一代通用任意波形/信號(hào)發(fā)生器的理想前端驅(qū)動(dòng)器。

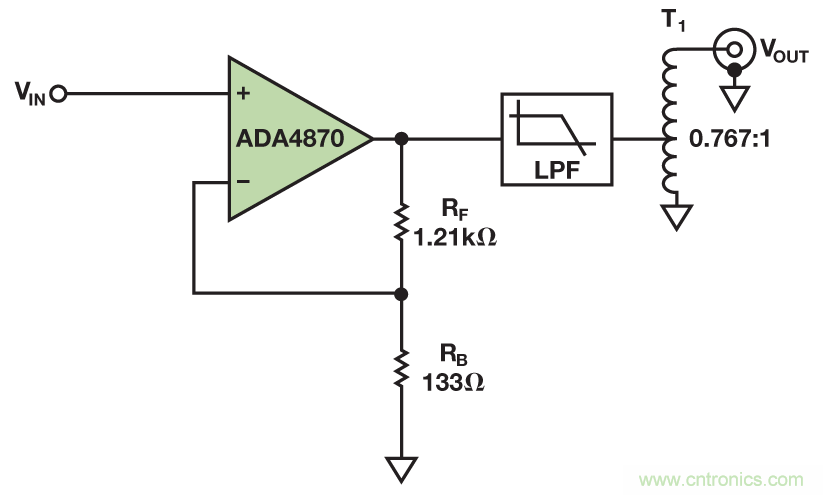

對于反射敏感型50 Ω 系統(tǒng)來說,ADA4870 要求一些無源器件使源阻抗與50 Ω 負(fù)載相匹配:一個(gè)阻性焊盤和一個(gè)1.5:1 RF 自動(dòng)變壓器。在1 V 裕量條件下,當(dāng)放大器有效負(fù)載為16 Ω 時(shí),可取得8 W 峰值功率。另外,如果反射不構(gòu)成問題,則可移除阻性焊盤,并用匝數(shù)比為0.77:1 的變壓器代替自動(dòng)變壓器。無阻性焊盤地,輸出功率增至16 W峰值(28.3 V 幅度)。

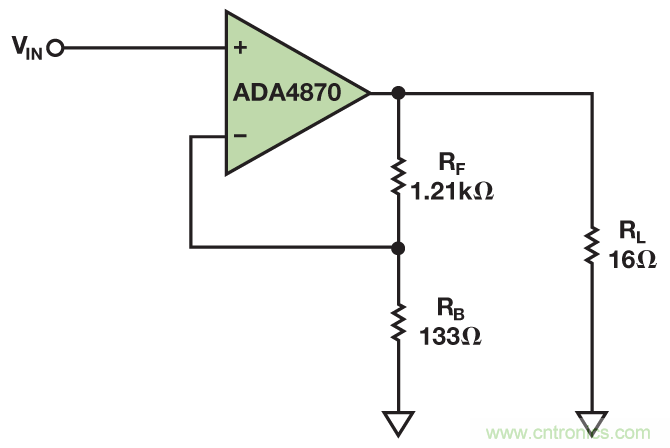

圖4. ADA4870 驅(qū)動(dòng)16 Ω(增益= 10)時(shí)的基本連接

為優(yōu)化輸出信號(hào)擺幅,我們將ADA4870 的增益倍數(shù)配置為10,因此,所需輸入幅度為1.6 V。ADA4870 有一個(gè)單端輸入,AD8338有一個(gè)差分輸出,因此,AD8130 差分接收放大器及其270 MHz增益帶寬積和1090 V/μs 壓擺率可同時(shí)提供差分至單端轉(zhuǎn)換和所需增益。AD8338 的輸出限制為±1.0 V,因此,AD8130 必須提供1.6 V/V 的中間增益。組合起來時(shí),三個(gè)器件形成一個(gè)完整的信號(hào)發(fā)生器輸出級(jí)。

圖5. 信號(hào)發(fā)生器輸出級(jí)

完成整個(gè)設(shè)計(jì)還需要最后兩個(gè)步驟:配置輸入網(wǎng)絡(luò)以實(shí)現(xiàn)最大輸入信號(hào)和抗混疊,設(shè)計(jì)輸出網(wǎng)絡(luò)以實(shí)現(xiàn)阻抗轉(zhuǎn)換。

AD8338 輸入網(wǎng)絡(luò)

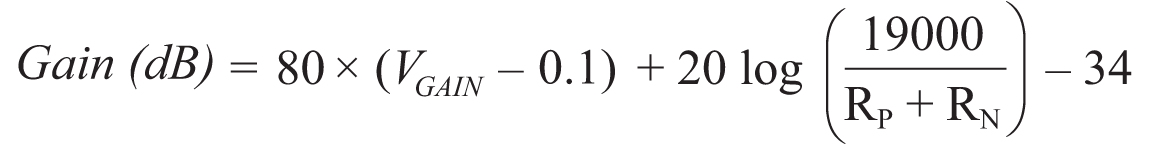

對于該設(shè)計(jì),差分輸出幅度為±1.0 V。在工廠默認(rèn)設(shè)置、內(nèi)部500 Ω電阻和最大增益條件下,輸入幅度一定是100 μV。通過向直接輸入引腳增加電阻,設(shè)計(jì)師可以調(diào)節(jié)該要求。由輸入電阻決定的增益范圍為:

(2)

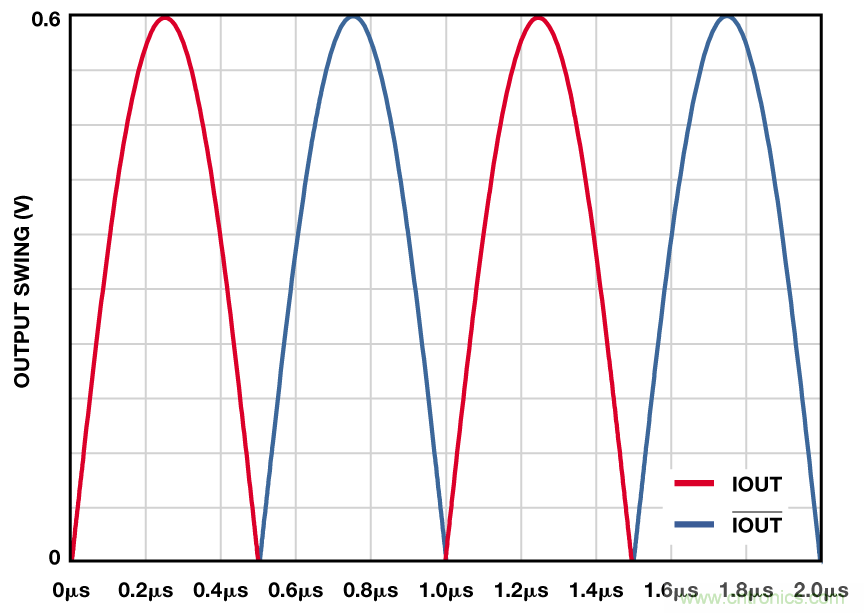

(2)在各輸入端使用40.2 kΩ 的電阻,可以在噪聲功率與輸入衰減之間 實(shí)現(xiàn)良好平衡。當(dāng)VGAIN = 1.1 V(最大增益)時(shí),增益為:

(3)

(3)此時(shí),差分輸入只需為21 mV。

當(dāng)VGAIN = 0.1 V 時(shí),增益為:

對于相同的21 mV 輸入,輸出約為100 μV。

考慮AD8130和ADA4870 的總增益,約為24.1 dB,ADA4870 的輸出幅度范圍為1.6 mV 至16 V。在阻性焊盤和自動(dòng)變壓器之后,輸出端的電壓將在2 mV 到20 V 之間。

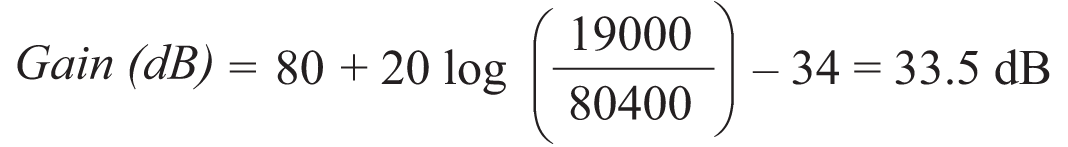

把AD8338 連接至DDS 等器件,要求考慮抗混疊和輸入衰減。例如,差分輸出AD9834CDDS 要求200 Ω 電阻接地,以實(shí)現(xiàn)正確的擺幅。每個(gè)輸出只會(huì)產(chǎn)生一半的正弦波信號(hào),如圖6 所示。

每個(gè)輸出峰值為0.6 V,使得有效輸入為±0.6 V,所需衰減為26 dB。在使用200 Ω 電阻時(shí),通過構(gòu)建簡單的電阻分壓器,可以輕松實(shí)現(xiàn)衰減。由于信號(hào)擺幅并不統(tǒng)一,因此,信號(hào)峰值應(yīng)該會(huì)達(dá)到預(yù)期衰減值。

圖6. 9834C IIOUT 和IIOUT的輸出擺幅。未顯示混疊偽像

(5)

(5)使用標(biāo)準(zhǔn)的6.98 Ω 和191 Ω 電阻值,結(jié)果會(huì)產(chǎn)生0.7%的誤差。

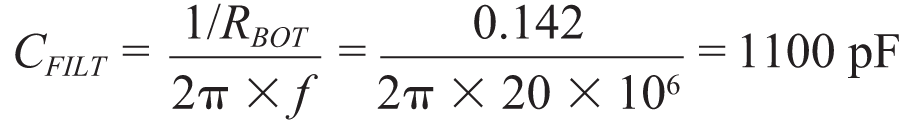

最后,需要一定的抗混疊處理。在75-MSPS 采樣速率下,奈奎斯特速率輸出為37.5 MHz,超過了該設(shè)計(jì)的20 MHz 帶寬。將抗混疊極點(diǎn)設(shè)為20 MHz,則所需電容為:

(6)

(6)這是一個(gè)標(biāo)準(zhǔn)值,因此,完整的輸入網(wǎng)絡(luò)如圖7 所示:

圖7. DDS + 衰減和濾波器網(wǎng)絡(luò) + AD8338

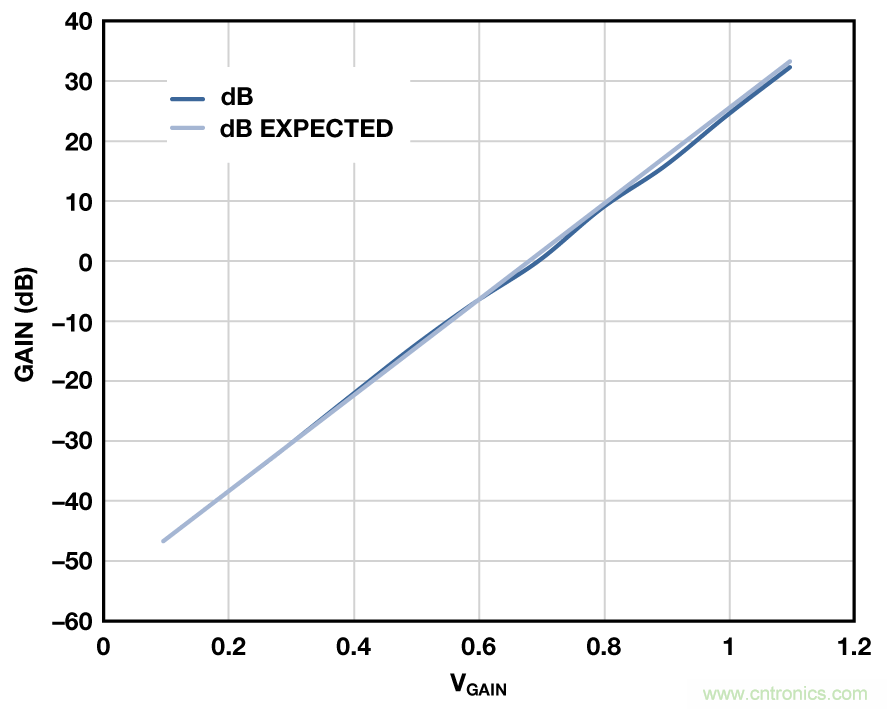

構(gòu)建該級(jí)并進(jìn)行測量。總體變化在±0.6 dB 之內(nèi),如圖8 所示。

圖8. AD8338 配置的計(jì)算所得增益和實(shí)測增益

ADA4870 輸出級(jí)

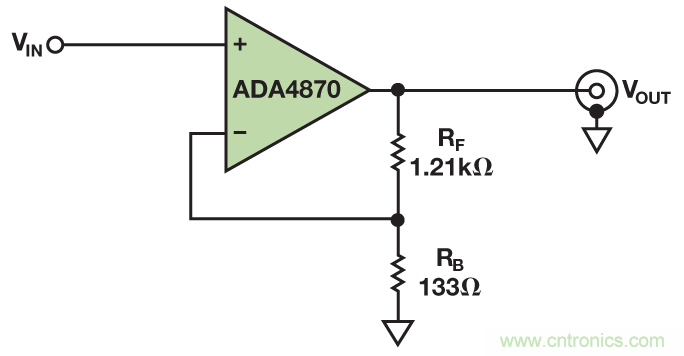

在單端輸出由AD8130 提供的情況下,ADA4870 將執(zhí)行最終10倍增益。設(shè)置該增益需要兩個(gè)電阻,無外部補(bǔ)償情況下,該級(jí)很穩(wěn)定。未完成的唯一工作是調(diào)整輸出網(wǎng)絡(luò),以滿足應(yīng)用需求。有三種通用實(shí)現(xiàn)方案:

1. 從放大器直接輸出至50 Ω

2. 填充自動(dòng)變壓器輸出至50 Ω

3. 未填充自動(dòng)變壓器輸出至50 Ω

對于直接輸出,放大器輸出直接連接輸出連接器,無需用任何網(wǎng)絡(luò)來轉(zhuǎn)換源,如圖9 所示。這種方法是真直流連接源的完美選擇,雖然不能發(fā)揮出器件的全部潛力,但仍然比典型信號(hào)發(fā)生器的10 V輸出幅度要好得多。在這種情況下,最大峰值功率為5.12 W。

圖9. 直接輸出驅(qū)動(dòng)連接

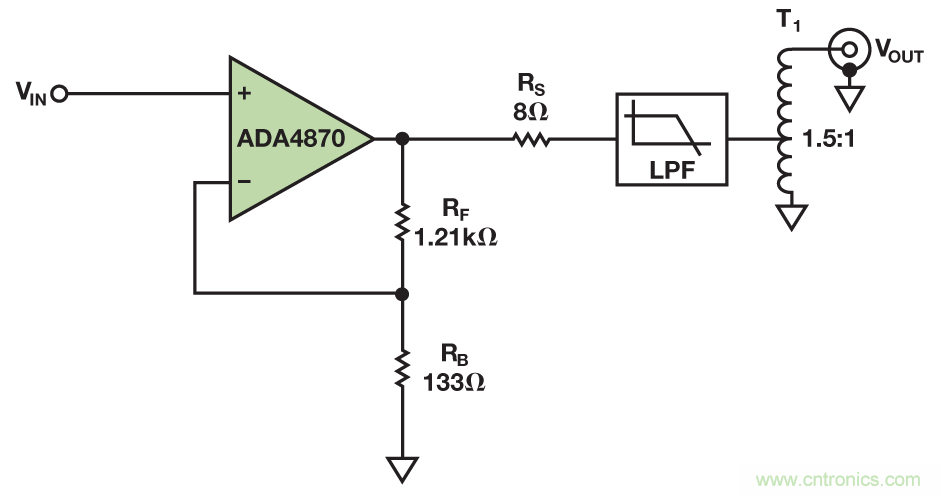

對于焊盤式設(shè)計(jì),16 Ω 負(fù)載在一個(gè)8 Ω 的串聯(lián)焊盤與經(jīng)濾波處理的1.5:1 自動(dòng)變壓器之間分配,如圖10 所示。在該模式下,由于設(shè)計(jì)具有低阻抗特性,因此,設(shè)計(jì)師使用的電感值可以比用于50 Ω設(shè)計(jì)的電感小6.25 倍。低通濾波器和自動(dòng)變壓器把8 Ω 有效源阻抗轉(zhuǎn)換成匹配良好的50 Ω 負(fù)載。這種設(shè)計(jì)方法的總峰值輸出功率為8 W,最適合需要50 Ω 匹配源的應(yīng)用,在這類應(yīng)用中,反射可能成為一個(gè)問題,比如,傳輸線路較長時(shí)。

圖10.焊盤式輸出設(shè)計(jì)的ADA4870 連接

在目標(biāo)頻段內(nèi),對于任何反射, 輸入阻抗均表現(xiàn)為50 Ω

最后一個(gè)選項(xiàng),也可能是信號(hào)發(fā)生器最有用的選項(xiàng),不使用8 Ω焊盤,而且輸出功率提高了一倍。我們?nèi)匀唤ㄗh使用LC 階梯式濾波器,如圖11 所示,但階梯值比用于50 Ω 系統(tǒng)(設(shè)計(jì)的標(biāo)稱阻抗為16 Ω)的值小3.125 倍。在這種情況下,自動(dòng)變壓器使用的匝數(shù)比為0.77:1。該模式下,峰值正弦波輸出幅度為28.3 V,ADA4870 將驅(qū)動(dòng)約16 W 至50 Ω 負(fù)載(8 W rms 或39 dBm)。

圖11. 用于驅(qū)動(dòng)50 Ω 負(fù)載的最佳功率輸出連接

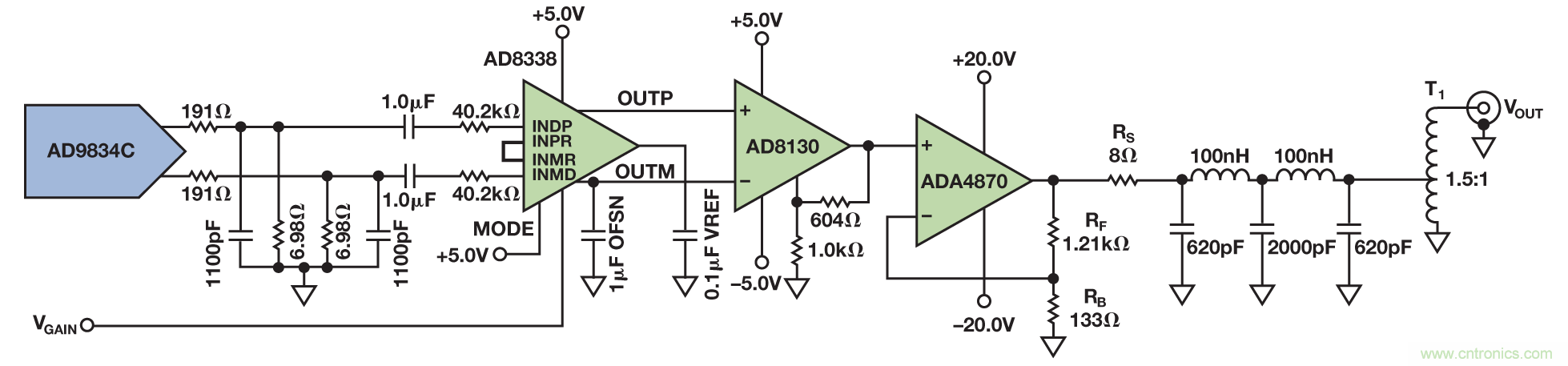

整體解決方案

在現(xiàn)實(shí)世界中,如果與真實(shí)世界不相符,仿真和等式毫無意義。因此,有必要構(gòu)建一個(gè)完整的系統(tǒng),基于預(yù)期值測量其性能。圖12 所示為一種實(shí)際焊盤式輸出設(shè)計(jì)的原理圖。

圖12. 完整的簡化原理圖

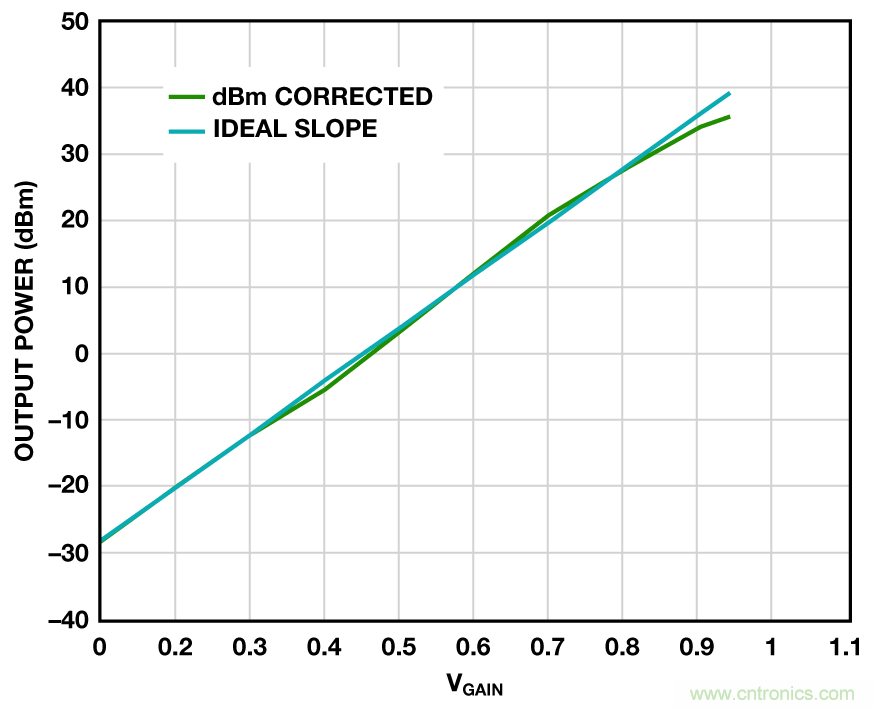

圖13 所示為無濾波器條件下的實(shí)測結(jié)果。系統(tǒng)增益一致性誤差為±1 dB,最差條件下輸出功率高達(dá)2.75 W rms(5.5 W 峰值)(P1dB壓縮點(diǎn),34 dBm)。值得注意的是,總增益范圍超過62 dB,范圍比許多標(biāo)準(zhǔn)發(fā)生器多16 dB。

圖13. 焊盤式、未濾波輸出功率結(jié)果。無濾波器時(shí),系統(tǒng)在36 dBm時(shí)出 現(xiàn)一個(gè)P1dB 點(diǎn)。FTEST = 14.0956 MHz

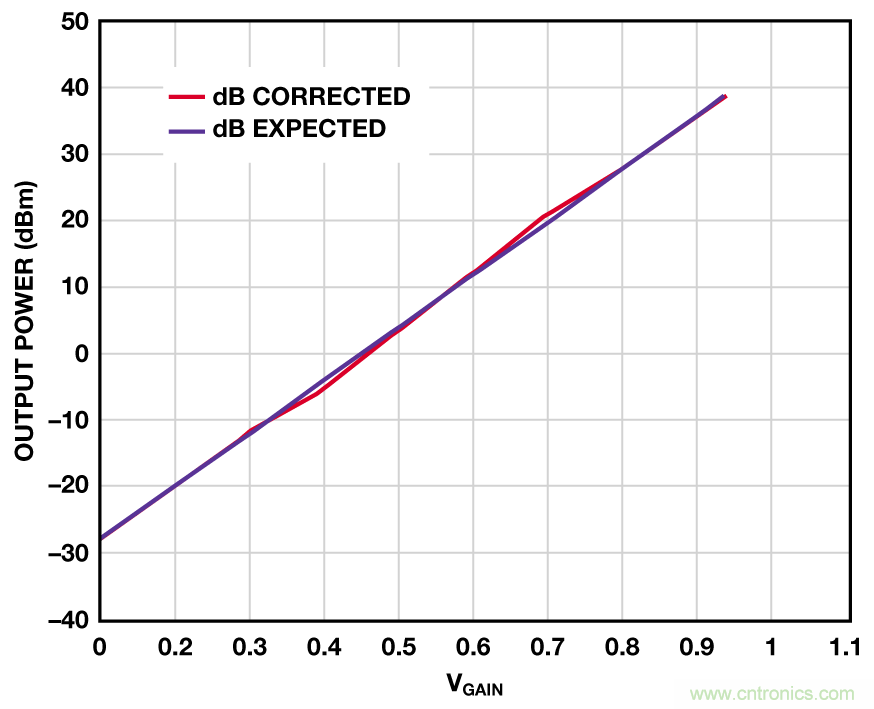

增益范圍可通過改善DDS 輸出端濾波機(jī)制以及降低系統(tǒng)噪聲的方式提高。圖14 所示為采用濾波器時(shí)的相同測量值。濾波輸出不存在同樣的P1dB 問題,結(jié)果將滿量程+36 dBm 輸出轉(zhuǎn)換成50 Ω負(fù)載??傇鲆婢€性度更佳(≤0.65 dB),誤差僅出現(xiàn)在中間電平周圍。

圖14. 5 階低通濾波器的實(shí)測輸出(fc = 20 MHz)。FTEST = 14.0956 MHz

如果具體運(yùn)行模式需要甚至更高的輸出功率,則針對給定應(yīng)用,可以將多個(gè)輸出放大用于驅(qū)動(dòng)專業(yè)變壓器。或者,可以將這里描述的設(shè)計(jì)方法用于電源較低的系統(tǒng),但這些方法必須符合替代設(shè)計(jì)的限制要求。

注意,受累積輸入衰減和增益誤差影響,測量上限止于VGAIN =0.9375 V。通過調(diào)整初始衰減網(wǎng)絡(luò),充分考慮總系統(tǒng)誤差,可以解決這個(gè)問題。校正后,總系統(tǒng)增益范圍將增至74 dB。

結(jié)論

配合高性能VGA 使用高性能、高輸出CFA,可以為新一代信號(hào)發(fā)生器構(gòu)建出一種簡單前端。這些器件的高度集成可以降低PCB電路板的總面積和成本。

要獲得更多功能,可以在閉環(huán)反饋系統(tǒng)中使用AD8310等對數(shù)放大器。增加對數(shù)放大器后,配合AD9834C 等DDS,設(shè)計(jì)師可以集成各種形式的包絡(luò)調(diào)制,如頻移鍵控(FSK)、開關(guān)鍵控(OOK)和相移鍵控(PSK),將其作為一項(xiàng)內(nèi)在功能;通過創(chuàng)造性地使用兩個(gè)基本模塊,實(shí)現(xiàn)不盡其數(shù)的選項(xiàng)。

參考電路

電流反饋放大器。

對數(shù)放大器/檢測器。

Signal Synthesis.

可變增益放大器(VGA)。

MT-034 指南,電流反饋(CFB)運(yùn)算放大器。

MT-057 指南,高速電流反饋運(yùn)算放大器。

MT-060 指南,在電壓反饋和電流反饋運(yùn)算放大器之間選擇。

MT-072 指南,精密可變增益放大器。

MT-073 指南,高速可變增益放大器。

推薦閱讀: