【導(dǎo)讀】低壓差穩(wěn)壓器(LDO)看似簡(jiǎn)單,但可提供重要功能�����,例如將負(fù)載與不干凈的電源隔離開(kāi)來(lái)或者構(gòu)建低噪聲電源來(lái)為敏感電路供電。

本簡(jiǎn)短教程介紹了一些常用的LDO 相關(guān)術(shù)語(yǔ)�����,以及一些基本概念�����,如壓差�����、裕量電壓�����、靜態(tài)電流�����、接地電流�����、關(guān)斷電流�����、效率�����、直流輸入電壓和負(fù)載調(diào)整率�����、輸入電壓和負(fù)載瞬態(tài)響應(yīng)�����、電源抑制比(PSRR)�����、輸出噪聲和精度�����。同時(shí),為了方便理解�����,文中采用了示例和插圖����。

設(shè)計(jì)過(guò)程中通常到后期才會(huì)進(jìn)行LDO 選型,并且很少進(jìn)行分析����。本文所述的概念將使設(shè)計(jì)人員能夠根據(jù)系統(tǒng)要求挑選最佳的LDO����。

壓差

壓差(VDROPOUT)是指輸入電壓進(jìn)一步下降而造成LDO 不再能進(jìn)行調(diào)節(jié)時(shí)的輸入至輸出電壓差。在壓差區(qū)域內(nèi)����,調(diào)整元件作用類似于電阻����,阻值等于漏極至源極導(dǎo)通電阻(RDSON)。壓差用RDSON和負(fù)載電流表示為:

VDROPOUT = ILOAD × RDSON

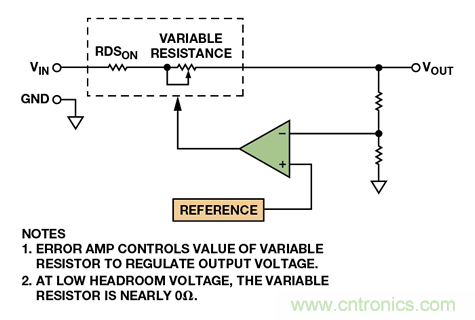

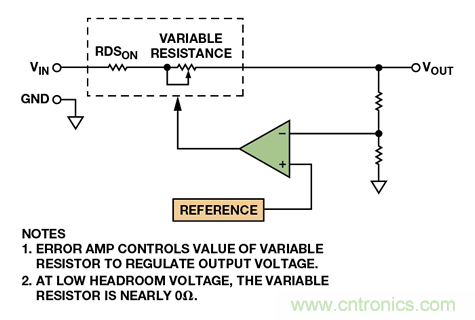

RDSON包括調(diào)整元件電阻����、片內(nèi)互連電阻����、引腳電阻和線焊電阻,并可通過(guò)LDO 的壓差進(jìn)行估算����。例如����,采用WLCSP 封裝時(shí)����,ADP151在200 mA負(fù)載下的最差情況壓差為200 mW����,因此RDSON約為1.0 Ω。圖1 所示為L(zhǎng)DO 的原理示意圖����。在壓差模式下����,可變電阻接近于零。LDO 無(wú)法調(diào)節(jié)輸出電壓����,因此輸入電壓和負(fù)載調(diào)整率����、精度、PSRR 和噪聲等其他參數(shù)都沒(méi)有意義����。

圖1. LDO 的原理示意圖

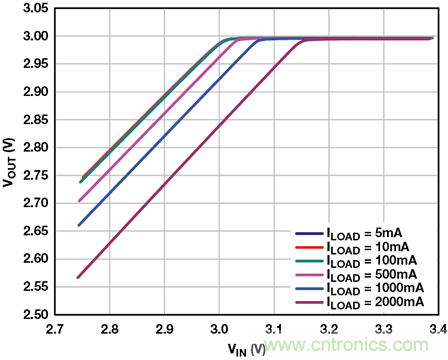

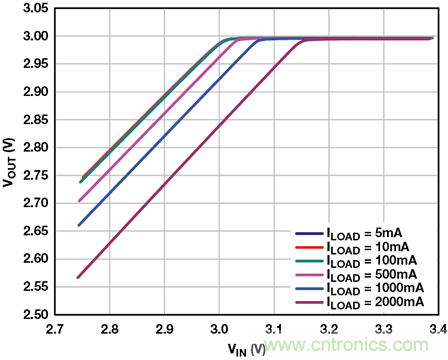

圖2 顯示了3.0 VADM7172LDO的輸出電壓與輸入電壓之間的關(guān)系。2 A 時(shí)的壓差通常為172 mW����,因此RDSON約為86 mΩ。壓差區(qū)域從約3.172 V 的輸入電壓下降到2.3 V����。低于2.3 V 時(shí)����,該器件不能正常工作。負(fù)載電流越小����,壓差也會(huì)按比例下降:在1 A時(shí)����,壓差為86 mV����。低壓差可最大程度地提高調(diào)節(jié)器的效率����。

圖2. 3.0 V ADM7172 LDO的壓差區(qū)

裕量電壓

裕量電壓是指LDO 滿足其規(guī)格所需的輸入至輸出電壓差����。數(shù)據(jù)手 冊(cè)通常將裕量電壓作為指定其他參數(shù)時(shí)所用的條件。裕量電壓通常約為400 mV 至500 mV����,但有些LDO 需要高達(dá)1.5 V 的裕量電壓����。裕量電壓不應(yīng)與壓差混淆,因?yàn)橹挥挟?dāng)LDO 在壓差模式下工作時(shí)這兩者才相同����。

靜態(tài)電流和接地電流

靜態(tài)電流(IQ)是指當(dāng)外部負(fù)載電流為零時(shí)為L(zhǎng)DO 的內(nèi)部電路供電所需的電流。它包括帶隙基準(zhǔn)電壓源����、誤差放大器、輸出分壓器以及過(guò)流和過(guò)溫檢測(cè)等電路的工作電流����。靜態(tài)電流由拓?fù)浣Y(jié)構(gòu)����、輸入電壓和溫度確定����。

IQ = IIN(空載時(shí))

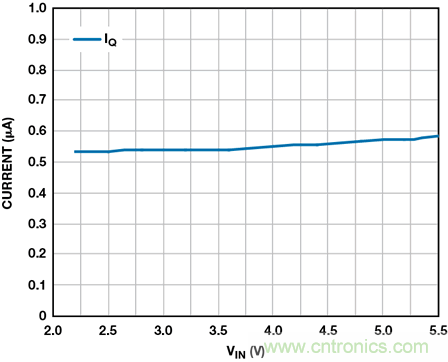

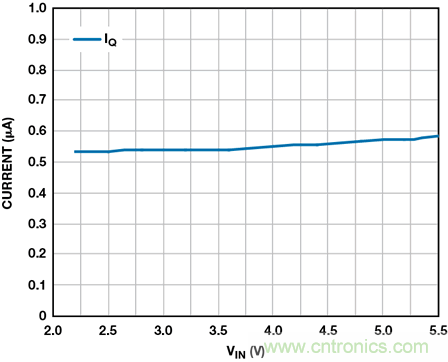

當(dāng)輸入電壓在2 V 和5.5 V 之間變化時(shí),ADP160 LDO 的靜態(tài)電流幾乎恒定不變����,如圖3 所示����。

圖3. ADP160 LDO的靜態(tài)電流與輸入電壓之間的關(guān)系

接地電流(IGND)是指輸入電流與輸出電流之差,并且必然包括靜態(tài)電流�����。低接地電流可最大程度地提高LDO 效率�����。

IGND= IIN– IOUT

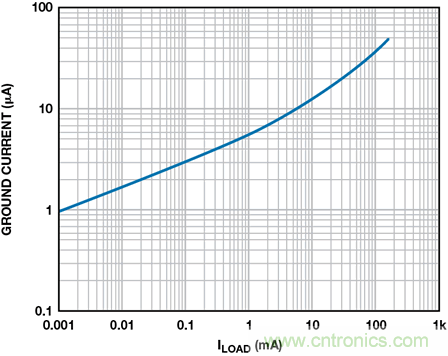

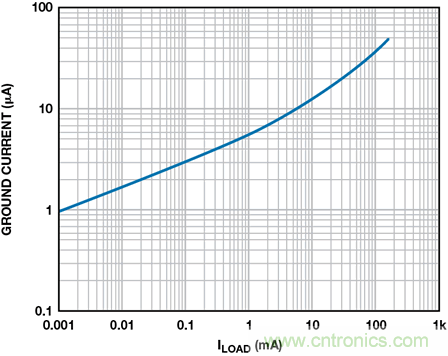

圖4 顯示了ADP160 LDO 的接地電流變化與負(fù)載電流之間的關(guān)系�����。

圖4. ADP160 LDO接地電流與負(fù)載電流之間的關(guān)系

對(duì)于高性能CMOS LDO�����,接地電流通常遠(yuǎn)小于負(fù)載電流的1%。接地電流隨負(fù)載電流的增加而增加�����,因?yàn)镻MOS 調(diào)整元件的柵極驅(qū)動(dòng)必須增加�����,以補(bǔ)償因其RON 引起的壓降�����。在壓差區(qū)域內(nèi)�����,在驅(qū)動(dòng)器級(jí)開(kāi)始飽和時(shí)�����,接地電流也會(huì)增加�����。對(duì)于要求具有低功耗或小偏置電流的應(yīng)用而言�����,CMOS LDO 至關(guān)重要�����。

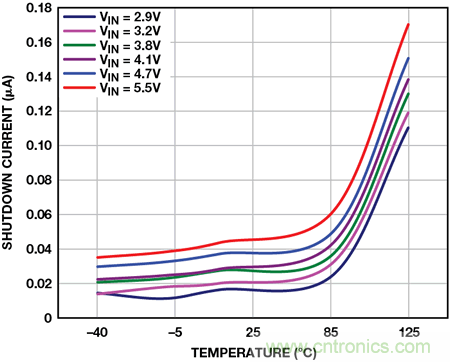

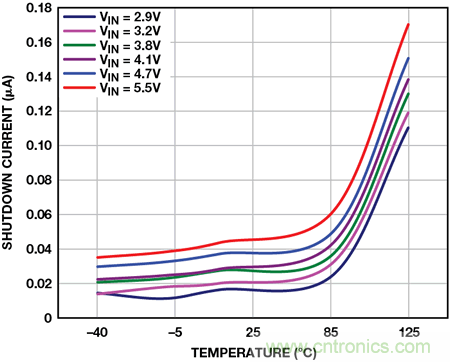

關(guān)斷電流

關(guān)斷電流是指輸出禁用時(shí)LDO 消耗的輸入電流�����。參考電路和誤差放大器在關(guān)斷模式下都不上電�����。較高的漏電流會(huì)導(dǎo)致關(guān)斷電流隨溫度升高而增加�����,如圖5 所示�����。

圖5. ADP160 LDO關(guān)斷電流與溫度之間的關(guān)系

效率

LDO 的效率由接地電流和輸入/輸出電壓確定:

效率 = IOUT/(IOUT + IGND) × VOUT/VIN × 100%

若需獲得較高的效率,必須最大程度地降低裕量電壓和接地電流�����。此外�����,還必須最大程度地縮小輸入和輸出之間的電壓差�����。輸入至輸出電壓差是確定效率的內(nèi)在因素�����,與負(fù)載條件無(wú)關(guān)�����。例如,采用5 V 電源供電時(shí)�����,3.3 V LDO 的效率從不會(huì)超過(guò)66%�����,但當(dāng)輸入電壓降至3.6 V 時(shí)�����,其效率將增加到最高91.7%。LDO 的功耗為(VIN – VOUT) × IOUT.

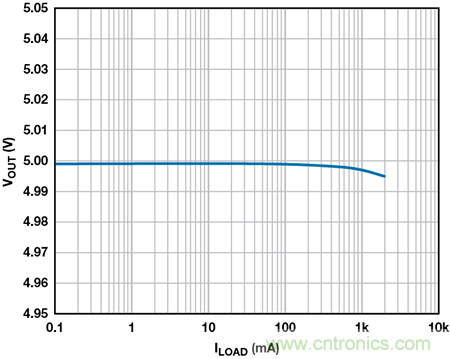

直流負(fù)載調(diào)整率

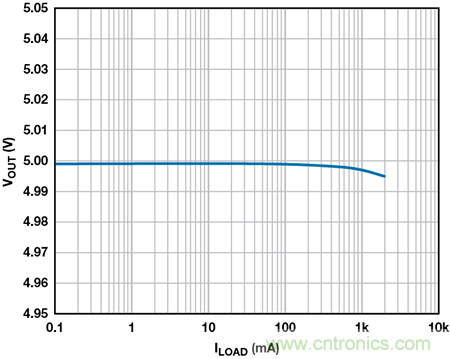

負(fù)載調(diào)整率衡量LDO 在負(fù)載條件變化時(shí)仍保持額定輸出電壓的能力�����。負(fù)載調(diào)整率定義如下(如圖6 所示):

負(fù)載調(diào)整率 = ?VOUT/?IOUT

圖6. ADM7172 LDO輸出電壓和負(fù)載電流之間的關(guān)系

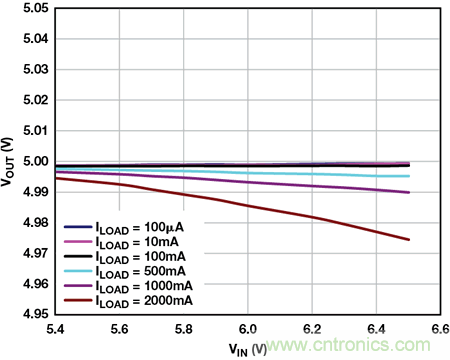

直流輸入電壓調(diào)整率

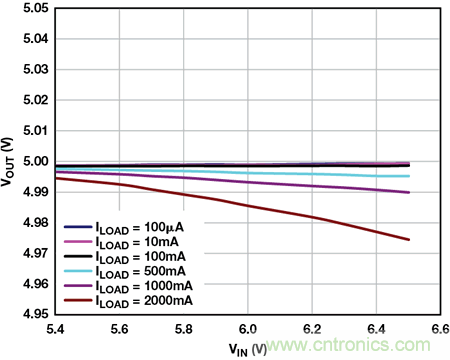

輸入電壓調(diào)整率是衡量LDO 在輸入電壓變化時(shí)仍保持規(guī)定輸出 電壓的能力�����。輸入電壓調(diào)整率定義為:

輸入電壓調(diào)整率 = ?VOUT/?VIN

圖7 顯示了不同負(fù)載電流條件下ADM7172的輸出電壓與輸入電壓之間的關(guān)系圖�����。輸入電壓調(diào)整率隨著負(fù)載電流增加而變差�����,原因是LDO 的總環(huán)路增益不斷降低。此外�����,LDO 的功耗也隨輸入至輸出電壓差增加而增加�����,這會(huì)導(dǎo)致結(jié)溫升高而使帶隙電壓和內(nèi)部失調(diào)電壓降低�����。

圖7. ADM7172 LDO輸出電壓和輸入電壓之間的關(guān)系

直流精度

整體精度會(huì)考慮輸入電壓和負(fù)載調(diào)整率�����、基準(zhǔn)電壓漂移和誤差放大器電壓漂移的影響�����。穩(wěn)壓電源上的輸出電壓變化主要是基準(zhǔn)電壓源和誤差放大器的溫度變化造成的�����。如果使用分立電阻來(lái)設(shè)置輸出電壓,這些電阻的容差可能是影響整體精度的最主要因素�����。輸入電壓和負(fù)載調(diào)整率與誤差放大器失調(diào)對(duì)整體精度的影響通常為1%至3%�����。

例如,可利用下列工作特性來(lái)計(jì)算3.3 V LDO 在0°C 至125°C 溫度范圍內(nèi)的總精度:電阻溫度系數(shù)為±100 ppm/°C�����,采樣電阻容差為±0.25%�����,因負(fù)載調(diào)整和輸入電壓調(diào)整而引起的輸出電壓變化分別為±10 mV 和±5 mV�����,并且基準(zhǔn)電壓源的精度為1%。

● 溫度導(dǎo)致的誤差 = 125°C × ±100 ppm/°C = ±1.25%

● 采樣電阻導(dǎo)致的誤差 = ±0.25%

● 負(fù)載調(diào)整率導(dǎo)致的誤差 = 100% × (±0.01 V/3.3 V) = ±0.303%

● 輸入電壓調(diào)整率導(dǎo)致的誤差 = 100% × (±0.005 V/3.3 V) = ±0.152%

● 基準(zhǔn)電壓源導(dǎo)致的誤差 = ±1%

最差情況誤差假定所有誤差都沿同一方向變化�����。

● 最差情況誤差 = ±(1.25% + 0.25% + 0.303% + 0.152% + 1%) = ±2.955%

典型誤差假定隨機(jī)變化�����,因此采用此誤差的平方根(rss)�����。

● 典型誤差 = ±√(1.252 + 0.252 + 0.3032 + 0.1522 + 12) = ±1.655%

LDO 從不會(huì)超過(guò)最差情況誤差�����,而rss 誤差是最有可能的誤差�����。誤差分布會(huì)以rss 誤差為中心并擴(kuò)展到在尾部包括最差情況誤差�����。

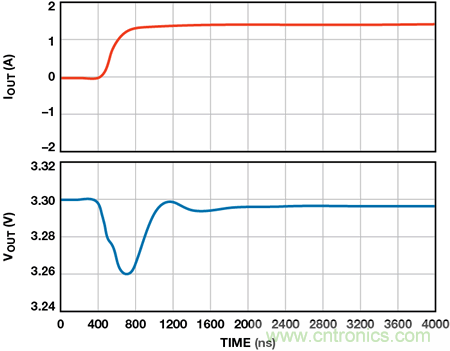

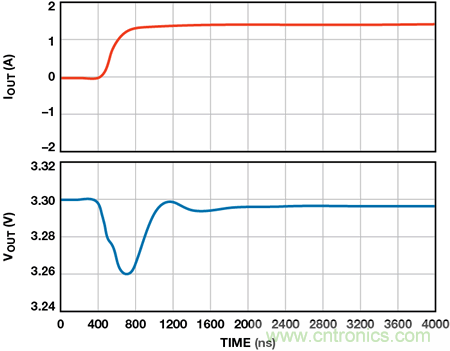

負(fù)載瞬態(tài)響應(yīng)

負(fù)載瞬態(tài)響應(yīng)是指負(fù)載電流階躍變化時(shí)的輸出電壓變化�����。它與輸出電容值�����、電容的等效串聯(lián)電阻(ESR)、LDO 控制環(huán)路的增益帶寬以及負(fù)載電流變化的大小和速率有關(guān)�����。

負(fù)載瞬態(tài)的變化速率會(huì)對(duì)負(fù)載瞬態(tài)響應(yīng)產(chǎn)生顯著影響。如果負(fù)載瞬態(tài)非常緩慢�����,比如100 mA/μs�����,LDO 的控制環(huán)路或許能夠跟蹤該變化�����。但是�����,如果負(fù)載瞬態(tài)較快,環(huán)路無(wú)法進(jìn)行補(bǔ)償�����,則可能會(huì)出現(xiàn)異常行為�����,例如因低相位裕量而導(dǎo)致過(guò)大的振鈴�����。

圖8 顯示了ADM7172 以3.75 A/μs 的變化速率對(duì)1 mA 至1.5 A 負(fù)載瞬態(tài)的響應(yīng)曲線�����。1.5 μs 的0.1%恢復(fù)時(shí)間和最小振鈴表明其具有良好的相位裕量�����。

圖8. ADM7172 負(fù)載瞬態(tài)響應(yīng)�����。400 ns 內(nèi)產(chǎn)生1 mA 至1.5 A 的負(fù)載階躍(紅線)�����。輸出電壓(藍(lán)線)

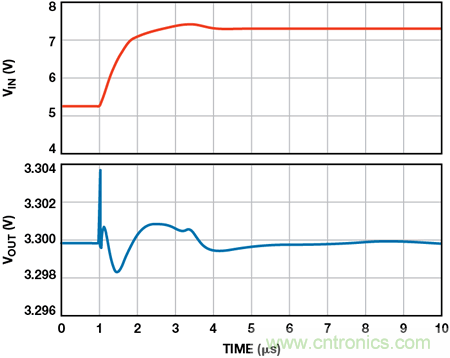

線路瞬態(tài)響應(yīng)

輸入電壓瞬態(tài)響應(yīng)是指輸入電壓階躍變化時(shí)的輸出電壓變化�����。它與LDO 控制環(huán)路的增益帶寬以及輸入電壓變化的大小和速率有關(guān)。

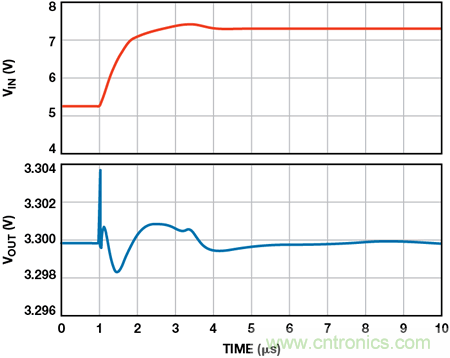

圖9 顯示了ADM7150 對(duì)2 V 輸入電壓階躍變化的響應(yīng)�����。輸出電壓偏差也顯示了環(huán)路帶寬和PSRR 的特性(參見(jiàn)下一部分)�����。對(duì)應(yīng)于1.5 μs 內(nèi)的2 V 變化�����,輸出電壓變化約為2 mV�����,表明約100 kHz時(shí)PSRR 約為60 dB�����。

同樣,跟在負(fù)載瞬態(tài)下一樣�����,輸入電壓的變化速率也對(duì)輸入瞬態(tài)響應(yīng)有較大的影響。當(dāng)輸入電壓緩慢變化(在LDO 的帶寬內(nèi)只出現(xiàn)一個(gè)凹陷)時(shí)�����,可隱藏振鈴或其他異常行為�����。

圖9. ADM7150 線路瞬態(tài)響應(yīng)�����。1.5 μs 內(nèi)產(chǎn)生5 V 至7 V 的線路階躍(紅線)。輸出電壓(藍(lán)線)

電源抑制

簡(jiǎn)單地說(shuō)�����,PSRR 衡量電路抑制電源輸入端出現(xiàn)的外來(lái)信號(hào)(噪聲和紋波)�����,使這些干擾信號(hào)不至于破壞電路輸出的性能�����。PSRR 定義為:

PSRR = 20 × log(VEIN/VEOUT)

其中�����,VEIN 和VEOUTT 分別是輸入端和輸出端出現(xiàn)的外來(lái)信號(hào)�����。

對(duì)于ADC、DAC 和放大器等電路�����,PSRR 適用于為內(nèi)部電路供電的輸入端�����。對(duì)于LDO�����,輸入電源引腳為內(nèi)部電路供電的同時(shí)也為輸出電壓供電�����。PSRR 具有與直流輸入電壓調(diào)整率相同的關(guān)系�����,但包括整個(gè)頻譜�����。

100 kHz 至1 MHz 范圍內(nèi)的電源抑制非常重要�����,因?yàn)長(zhǎng)DO 經(jīng)常跟高效的開(kāi)關(guān)電源配合使用來(lái)為敏感的模擬電路供電�����。

LDO 的控制環(huán)路往往是確定電源抑制性能的主要因素�����。同時(shí)大容量、低ESR 的電容也對(duì)電源抑制性能非常有用�����,特別是在頻率超過(guò)控制環(huán)路增益帶寬的情況下。

PSRR 與頻率的關(guān)系

PSRR 不是通過(guò)單一值來(lái)定義�����,因?yàn)樗c頻率相關(guān)�����。LDO 由基準(zhǔn)電壓源、誤差放大器�����,以及MOSFET 或雙極性晶體管等功率調(diào)整元件組成�����。誤差放大器提供直流增益以便調(diào)節(jié)輸出電壓�����。誤差放大器的交流增益特性在很大程度上決定了PSRR�����。典型LDO 在10 Hz 時(shí)可具有高達(dá)80 dB 的PSRR�����,但在數(shù)十kHz 時(shí)則可降至僅20 dB�����。

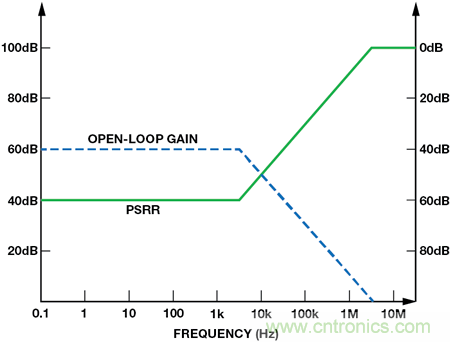

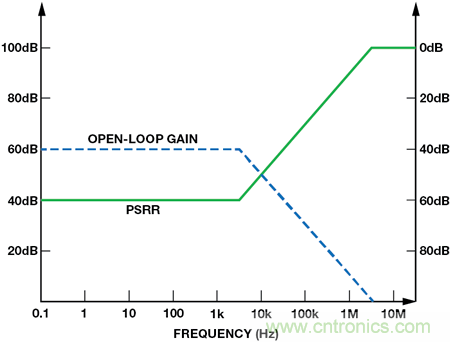

圖10 顯示了誤差放大器的增益帶寬和PSRR 之間的關(guān)系�����。這是一個(gè)簡(jiǎn)化的示例,圖中忽略了輸出電容和調(diào)整元件的寄生效應(yīng)�����。PSRR 為開(kāi)環(huán)增益的倒數(shù)�����,直到3 kHz 時(shí)增益開(kāi)始下降為止�����。然后�����,PSRR 以20 dB/十倍頻程的速率降低�����,直到3 MHz 時(shí)達(dá)到0 dB�����。

圖10. LDO 增益與PSRR 的簡(jiǎn)化關(guān)系圖

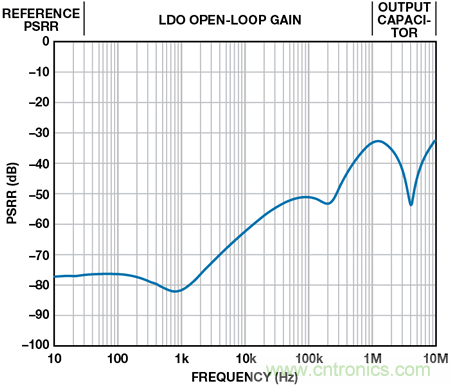

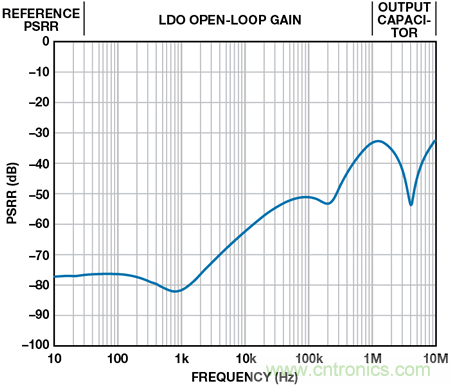

圖11 顯示了用來(lái)表征LDO PSRR 的三個(gè)主要頻域:基準(zhǔn)電壓PSRR 區(qū)�����、開(kāi)環(huán)增益區(qū)和輸出電容區(qū)�����?����;鶞?zhǔn)電壓PSRR 區(qū)取決于參考放大器的PSRR 和LDO 的開(kāi)環(huán)增益�����。理想情況下�����,參考放大器需與電源擾動(dòng)完全隔離�����,但實(shí)際上,參考放大器只需抑制最高數(shù)十Hz 的電源噪聲�����,因?yàn)檎`差放大器反饋電路能確保在低頻時(shí)具有高PSRR�����。

圖11. 典型LDO PSRR 與頻率的關(guān)系

在大約10 Hz 以上的第二區(qū)中,PSRR 主要由LDO 的開(kāi)環(huán)增益決定�����。此區(qū)中的PSRR 取決于誤差放大器的增益帶寬(最高為單位增益頻率)�����。在低頻時(shí)�����,誤差放大器的交流增益等于直流增益�����。增益保持不變�����,直至達(dá)到3 dB 截止頻率�����。在高于3 dB 截止頻率下,誤差放大器的交流增益隨著頻率增加而降低�����,速率通常為20 dB/十倍頻程�����。

在誤差放大器的單位增益頻率以上�����,控制環(huán)路的反饋對(duì)PSRR 沒(méi)有影響,此時(shí)PSRR 由輸出電容和輸入與輸出電壓之間的任何寄生效應(yīng)確定。在這些頻率下�����,PSRR 主要受輸出電容的ESR�����,ESL以及電路板布局布線的影響�����。為了降低任何高頻諧振的影響,必須特別注意布局布線�����。

PSRR 與負(fù)載電流的關(guān)系

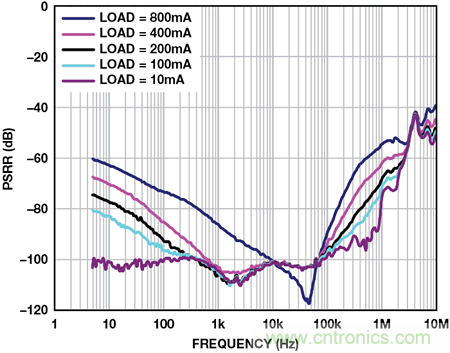

負(fù)載電流影響誤差放大器反饋環(huán)路的增益帶寬�����,因此也會(huì)影響PSRR�����。在低負(fù)載電流下(通常小于50 mA)�����,調(diào)整元件的輸出阻抗很高�����。由于控制環(huán)路的負(fù)反饋�����,LDO 的輸出近乎是理想的電流源�����。輸出電容和調(diào)整元件形成的極點(diǎn)出現(xiàn)在相對(duì)較低的頻率,因此�����,PSRR 在低頻條件下往往會(huì)提高�����。低電流時(shí)輸出級(jí)的高直流增益往往也會(huì)提高誤差放大器單位增益點(diǎn)以下各頻率的PSRR�����。

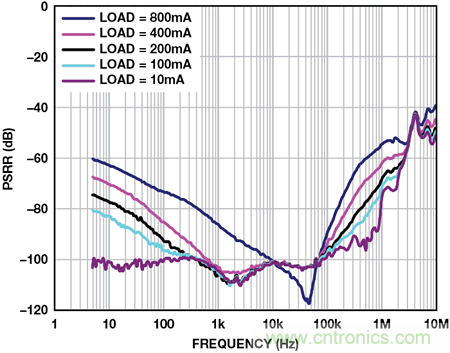

在高負(fù)載電流下�����,LDO 輸出不能近似成一個(gè)理想電流源。調(diào)整元件的輸出阻抗會(huì)下降�����,從而導(dǎo)致輸出級(jí)的增益降低�����,DC 至反饋環(huán)路單位增益頻率之間的PSRR 會(huì)有所下降�����。當(dāng)負(fù)載電流增加時(shí)�����,PSRR 會(huì)急劇下降�����,如圖12 所示�����。當(dāng)負(fù)載電流從400 mA 增加到800 mA 時(shí),ADM7150的PSRR 在1 kHz 時(shí)降低了20 dB�����。

輸出級(jí)帶寬隨輸出極點(diǎn)頻率的升高而增加�����。在高頻條件下�����,PSSR應(yīng)會(huì)隨帶寬增加而提高�����,但實(shí)際上�����,由于總環(huán)路增益降低,高頻PSRR 可能不會(huì)提高�����。一般而言�����,輕載時(shí)的PSRR 優(yōu)于重載時(shí)�����。

圖12. ADM7150 電源抑制與頻率的關(guān)系(VOUT = 5 V�����,VIN = 6.2 V)/figcaption>

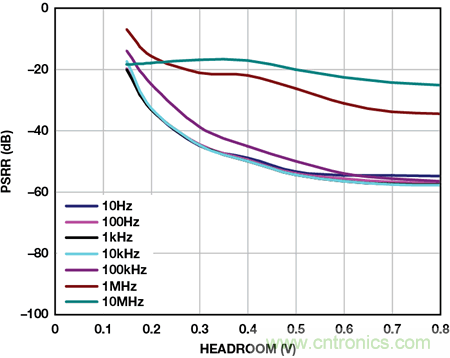

PSRR 與LDO 裕量的關(guān)系

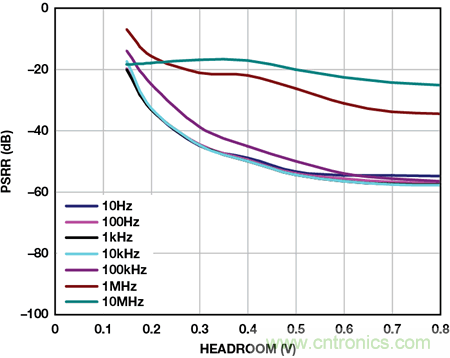

PSRR 也與輸入到輸出電壓差(即裕量)有關(guān)�����。對(duì)于固定裕量電壓�����,PSRR 隨著負(fù)載電流的增加而降低�����;這在高負(fù)載電流和小裕量電壓時(shí)尤其明顯。圖13 顯示了5 V ADM7172 在2 A 負(fù)載下PSRR 與裕量電壓之間的關(guān)系差異�����。

隨著負(fù)載電流增加�����,調(diào)整元件(ADM7172 的PMOSFET)脫離飽和狀態(tài)�����,進(jìn)入線性工作區(qū)�����,其增益相應(yīng)地降低�����。這導(dǎo)致LDO的總環(huán)路增益降低�����,因而PSRR 下降�����。裕量電壓越小�����,增益降幅越大。在某些小裕量電壓下�����,控制環(huán)路根本沒(méi)有增益�����,PSRR 幾乎會(huì)降至0�����。

導(dǎo)致環(huán)路增益降低的另一個(gè)因素是調(diào)整元件的非零電阻RDSON�����。負(fù)載電流在RDSON 上引起的任何壓降都會(huì)導(dǎo)致調(diào)整元件有效裕量降低�����。例如�����,如果調(diào)整元件是一個(gè)1 Ω 的器件�����,當(dāng)負(fù)載電流為200 mA時(shí)�����,裕量將降低200 mV�����。當(dāng)LDO 在1 V 或更低的裕量電壓下工作時(shí)�����,估算PSRR 時(shí)必須考慮此壓降。

在壓差模式下�����,PSRR 是由RDSON 和輸出電容形成的極點(diǎn)決定的�����。在非常高的頻率下,PSRR 會(huì)受輸出電容ESR 與RDSON 的比值限制�����。

圖13. ADM7172 電源抑制與裕量的關(guān)系(VOUT = 5 V�����,2 A 負(fù)載電流)

比較LDO PSRR 規(guī)格

比較LDO 的PSRR 規(guī)格時(shí)�����,應(yīng)確保測(cè)量是在相同的測(cè)試條件下進(jìn)行的�����。許多舊式LDO 僅指定120 Hz 或1 kHz 時(shí)的PSRR�����,而未提及裕量電壓或負(fù)載電流�����。至少�����,電氣技術(shù)規(guī)格表中的PSRR 應(yīng)針對(duì)不同的頻率列出�����。為使比較有意義,最好應(yīng)使用不同負(fù)載和裕量電壓下的PSRR 典型工作性能曲線�����。

輸出電容也會(huì)影響高頻時(shí)的LDO PSRR�����。例如�����,1 μF 電容的阻抗是10 μF 電容的10 倍�����。在頻率高于誤差放大器的單位增益交越頻率時(shí)�����,電源噪聲的衰減與輸出電容有關(guān)�����,此時(shí)電容值就特別重要�����。比較PSRR 數(shù)據(jù)時(shí)�����,輸出電容的類型和值必須相同�����,否則比較無(wú)效�����。

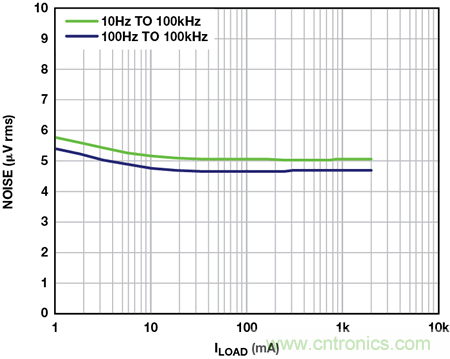

輸出噪聲電壓

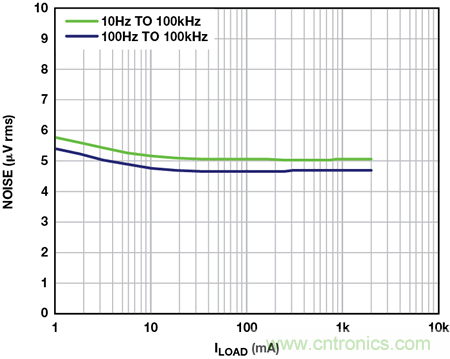

輸出噪聲電壓是指在恒定輸出電流和無(wú)紋波輸入電壓條件下�����,給定頻率范圍(通常為10 Hz 或100 Hz 至100 kHz)上的RMS 輸出噪聲電壓�����。LDO 的主要輸出噪聲源是內(nèi)部基準(zhǔn)電壓源和誤差放大器?����,F(xiàn)代LDO 采用數(shù)十nA 的內(nèi)部偏置電流工作,以便實(shí)現(xiàn)15μA或更低的靜態(tài)電流�����。這些低偏置電流要求使用高達(dá)GΩ 級(jí)的偏置電阻�����。輸出噪聲的典型范圍為5 μ V r ms 至100 μV rms�����。圖14 顯示了ADM7172 輸出噪聲與負(fù)載電流之間的關(guān)系�����。

ADM7172 等部分LDO 可使用外部電阻分壓器來(lái)設(shè)置初始設(shè)定點(diǎn)以上的輸出電壓�����,使初始設(shè)定為1.2 V 的器件可提供3.6 V 輸出電壓�����。對(duì)于這樣的應(yīng)用�����,可向該分壓器添加降噪網(wǎng)絡(luò)�����,以便使輸出噪聲恢復(fù)到接近初始固定電壓的水平�����。

圖14. ADM7172 輸出噪聲與負(fù)載電流之間的關(guān)系

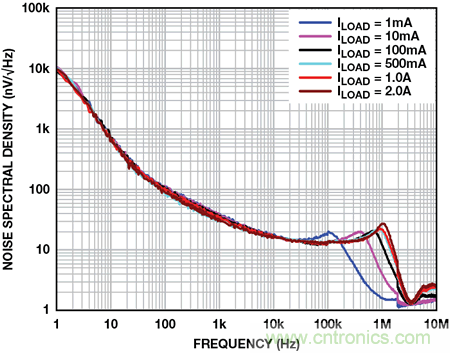

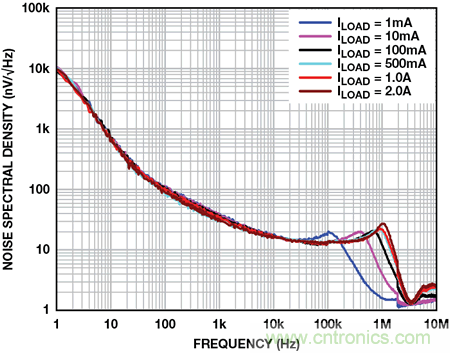

LDO 輸出噪聲的另一種表示方式是噪聲頻譜密度�����。在寬頻率范圍內(nèi)繪制給定頻率下1 Hz 帶寬上的rms 噪聲曲線圖�����,然后使用該信息來(lái)計(jì)算給定頻率帶寬下的rms 噪聲�����。圖15 顯示了ADM7172 在1 Hz 到10 MHz 范圍內(nèi)的噪聲頻譜密度�����。

圖15. ADM7172 噪聲頻譜密度與負(fù)載電流之間的關(guān)系

結(jié)論

LDO 看似簡(jiǎn)單實(shí)則非常重要。若要正確運(yùn)用這些LDO 并獲得最佳結(jié)果�����,必須綜合考慮很多因素�����。對(duì)常用LDO 術(shù)語(yǔ)有個(gè)基本了解后�����,設(shè)計(jì)工程師便可有效運(yùn)用數(shù)據(jù)手冊(cè)來(lái)確定對(duì)于設(shè)計(jì)而言最為重要的參數(shù)�����。

推薦閱讀: