【導(dǎo)讀】在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,電容所處的位置不同,稱呼就不一樣了。對(duì)于同一個(gè)電路來說,旁路(bypass)電容是把輸入信號(hào)中的高頻噪聲作為濾除對(duì)象,把前級(jí)攜帶的高頻雜波濾除,而去耦(decoupling)電容也稱退耦電容,是把輸出信號(hào)的干擾作為濾除對(duì)象。

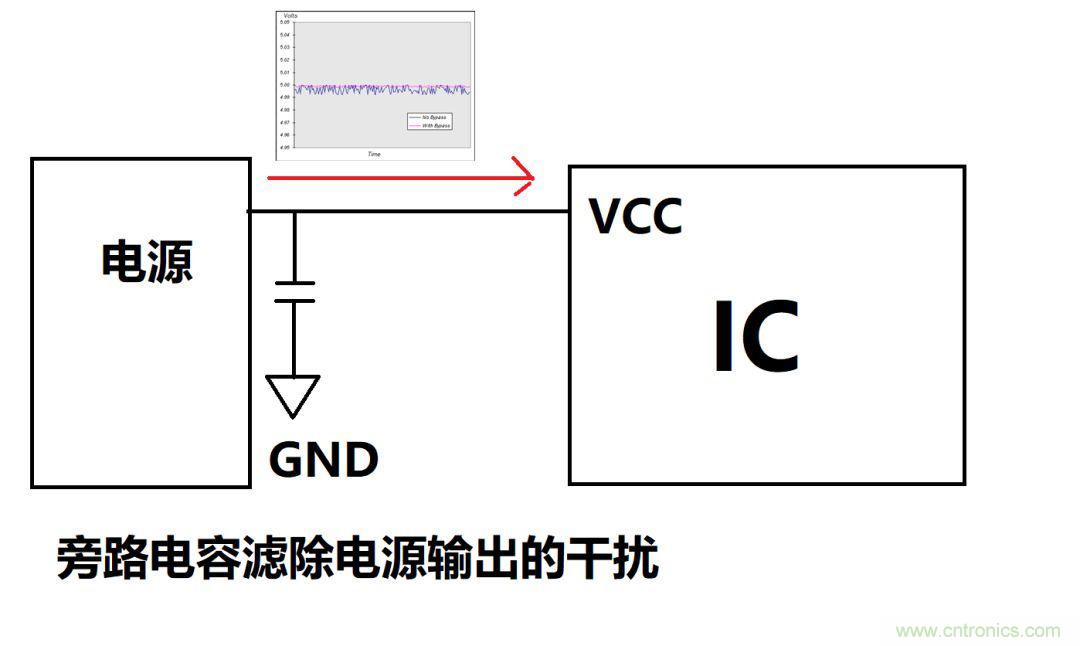

旁路電容是把電源或者輸入信號(hào)中的交流分量的干擾作為濾除對(duì)象。

有了旁路電容,將電源5V中的交流分量——波動(dòng)進(jìn)行濾除。將藍(lán)色波形變成粉紅色波形。一般來說,靠近電源放置。

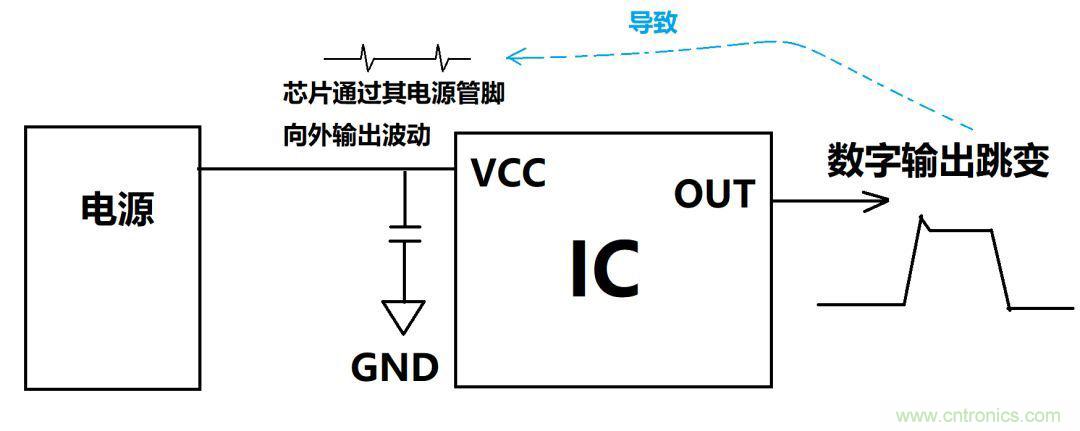

去耦電容是芯片的電源管腳,由于自身用電過程中信號(hào)跳變產(chǎn)生的電源管腳對(duì)外的波形輸出,我們用電容進(jìn)行濾除。

把信號(hào)電源管腳,輸出干擾作為濾除對(duì)象,防止干擾信號(hào)返回電源。

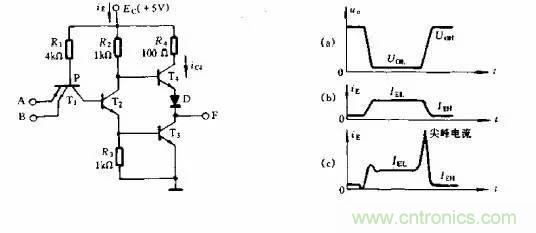

尖峰電流的形成:

數(shù)字電路輸出高電平時(shí)從電源拉出的電流Ioh和低電平輸出時(shí)灌入的電流Iol的大小一般是不同的,即:Iol>Ioh。以下圖的TTL與非門為例說明尖峰電流的形成:

輸出電壓如右圖(a)所示,理論上電源電流的波形如右圖(b),而實(shí)際的電源電流保險(xiǎn)如右圖(c)。由圖(c)可以看出在輸出由低電平轉(zhuǎn)換到高電平時(shí)電源電流有一個(gè)短暫而幅度很大的尖峰。尖峰電源電流的波形隨所用器件的類型和輸出端所接的電容負(fù)載而異。

產(chǎn)生尖峰電流的主要原因是:

輸出級(jí)的T3、T4管短設(shè)計(jì)內(nèi)同時(shí)導(dǎo)通。在與非門由輸出低電平轉(zhuǎn)向高電平的過程中,輸入電壓的負(fù)跳變在T2和T3的基極回路內(nèi)產(chǎn)生很大的反向驅(qū)動(dòng)電流,由于T3的飽和深度設(shè)計(jì)得比T2大,反向驅(qū)動(dòng)電流將使T2首先脫離飽和而截止。T2截止后,其集電極電位上升,使T4導(dǎo)通??墒谴藭r(shí)T3還未脫離飽和,因此在極短得設(shè)計(jì)內(nèi)T3和T4將同時(shí)導(dǎo)通,從而產(chǎn)生很大的ic4,使電源電流形成尖峰電流。圖中的R4正是為了限制此尖峰電流而設(shè)計(jì)。

這應(yīng)該是他們的本質(zhì)區(qū)別。去耦電容相當(dāng)于電池,避免由于電流的突變而使電壓下降,相當(dāng)于濾紋波。具體容值可以根據(jù)電流的大小、期望的紋波大小、作用時(shí)間的大小來計(jì)算。去耦電容一般都很大,對(duì)更高頻率的噪聲,基本無效。旁路電容就是針對(duì)高頻來的,也就是利用了電容的頻率阻抗特性。只是旁路電容一般是指高頻旁路,也就是給高頻的開關(guān)噪聲提高一條低阻抗泄防途徑。高頻旁路電容一般比較小,根據(jù)諧振頻率一般是0.1u,0.01u等 ,而去耦合電容一般比較大,是10u或者更大,依據(jù)電路中分布參數(shù),以及驅(qū)動(dòng)電流的變化大小來確定。

旁路電容

旁路電容(bypass)是把輸入信號(hào)中的高頻噪聲作為濾除對(duì)象,把前級(jí)攜帶的高頻雜波濾除。

旁路電容的主要功能是產(chǎn)生一個(gè)交流分路,從而消去進(jìn)入易感區(qū)的那些不需要的能量。旁路電容一般作為高頻旁路器件來減小對(duì)電源模塊的瞬態(tài)電流需求。 通常鋁電解電容和鉭電 容比較適合作旁路電容,其電容值取決于PCB板上的瞬態(tài)電流需求,一般在10至470µF范圍內(nèi)。

去耦電容

去耦電容(decoupling)也稱退耦電容,是把芯片的電源腳的輸出的干擾作為濾除對(duì)象。去耦電容在集成電路電源和地之間的有兩個(gè)作用:一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲(電容對(duì)高頻阻抗小,將之瀉至GND)。

數(shù)字電路中,當(dāng)電路從一個(gè)狀態(tài)轉(zhuǎn)換為另一種狀態(tài)時(shí),就會(huì)在電源線上產(chǎn)生一個(gè)很大的尖峰電流,形成瞬變的噪聲電壓,會(huì)影響前級(jí)的正常工作。這就是耦合。對(duì)于噪聲能力弱、關(guān)斷時(shí)電流變化大的器件和ROM、RAM等存儲(chǔ)型器件,應(yīng)在芯片的電源線(Vcc)和地線(GND)間直接接入去耦電容。

數(shù)字電路中典型的去耦電容值是0.1µF。這個(gè)電容的分布電感的典型值是5µH。 0.1µF的去耦電容有5µH的分布電感,它的并行共振頻率大約在7MHz左右,也就是說,對(duì)于10MHz以 下的噪聲有較好的去耦效果,對(duì)40MHz以上的噪聲幾乎不起作用。 1µF、10µF的電容,并行共振頻率在20MHz以上,去除高頻噪聲的效果要好一些。 每10片左右集成電路要加一片充放電電容,或1個(gè)蓄能電容,可選10µF左右。最好不用電解電容,電解電容是兩層薄膜卷起來的,這種卷起來的結(jié)構(gòu)在高頻時(shí)表現(xiàn)為電感。要使用 鉭電容或聚碳酸酯電容。去耦電容的選用并不嚴(yán)格,可按C=1/F,即10MHz取0.1µF,100MHz取0.01µ。

案例分析:

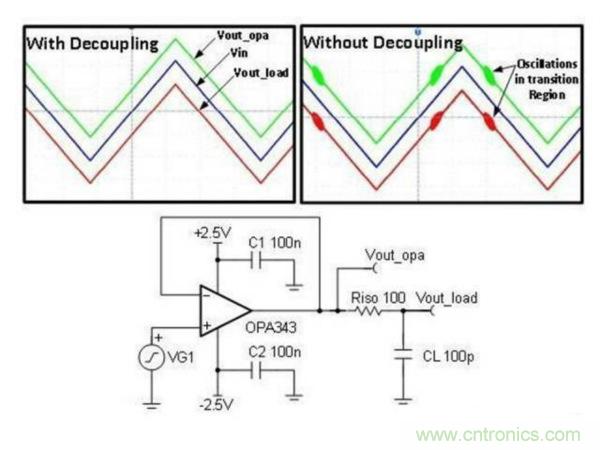

采用去耦和不采用去耦的緩沖電路(測量結(jié)果)

為帶去耦電容器和不帶去耦電容器(C1 和C2)情況下用于驅(qū)動(dòng) R-C 負(fù)載的緩沖電路。我們注意到,在不使用去耦電容器的情況下,電路的輸出信號(hào)包含高頻 (3.8MHz) 振蕩。對(duì)于沒有去耦電容器的放大器而言,通常會(huì)出現(xiàn)穩(wěn)定性低、瞬態(tài)響應(yīng)差、啟動(dòng)出現(xiàn)故障以及其它多種異常問題。

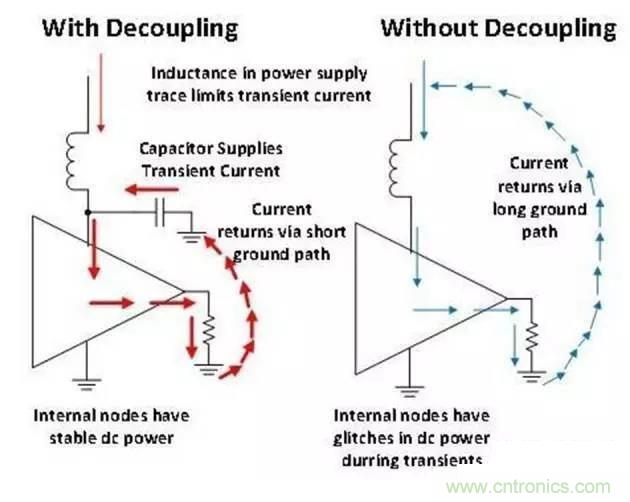

帶去耦合和不帶去耦合情況下的電流

電源線跡的電感將限制暫態(tài)電流。去耦電容與器件非常接近,因此電流路徑的電感很小。在暫態(tài)過程中,該電容器可在非常短的時(shí)間內(nèi)向器件提供超大量的電流。未采用去耦電容的器件無法提供暫態(tài)電流,因此放大器的內(nèi)部節(jié)點(diǎn)會(huì)下垂(通常稱為干擾)。無去耦電容的器件其內(nèi)部電源干擾會(huì)導(dǎo)致器件工作不連續(xù),原因是內(nèi)部節(jié)點(diǎn)未獲得正確的偏置。

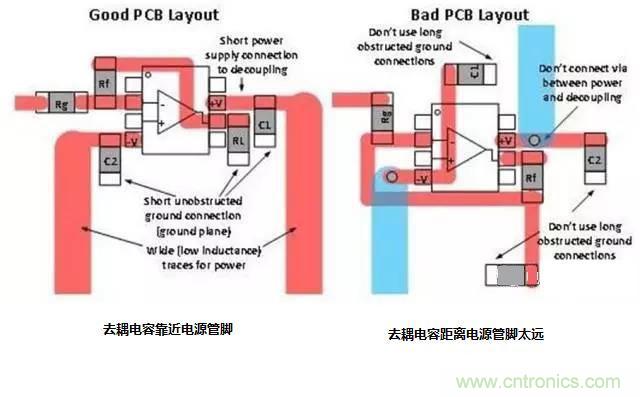

良好與糟糕 PCB 板面布局的對(duì)比

除了使用去耦電容器外,還要在去耦電容器、電源和接地端之間采取較短的低阻抗連接。將良好的去耦合板面布局與糟糕的布局進(jìn)行了對(duì)比。應(yīng)始終嘗試著讓去耦合連接保持較短的距離,同時(shí)避免在去耦合路徑中出現(xiàn)通孔,原因是通孔會(huì)增加電感。大部分產(chǎn)品說明書都會(huì)給出去耦合電容器的推薦值。如果沒有給出,則可以使用 0.1uF。

PCB布局時(shí)去耦電容擺放

對(duì)于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠(yuǎn),最外層放置容值最大的。但是,所有對(duì)該芯片去耦的電容都盡量靠近芯片。

下面的圖1就是一個(gè)擺放位置的例子。本例中的電容等級(jí)大致遵循10倍等級(jí)關(guān)系。

還有一點(diǎn)要注意,在放置時(shí),最好均勻分布在芯片的四周,對(duì)每一個(gè)容值等級(jí)都要這樣。通常芯片在設(shè)計(jì)的時(shí)候就考慮到了電源和地引腳的排列位置,一般都是均勻分布在芯片的四個(gè)邊上的。因此,電壓擾動(dòng)在芯片的四周都存在,去耦也必須對(duì)整個(gè)芯片所在區(qū)域均勻去耦。如果把上圖中的680pF電容都放在芯片的上部,由于存在去耦半徑問題,那么就不能對(duì)芯片下部的電壓擾動(dòng)很好的去耦。

電容的安裝

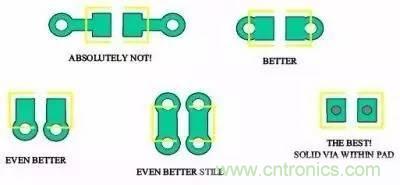

在安裝電容時(shí),要從焊盤拉出一小段引出線,然后通過過孔和電源平面連接,接地端也是同樣。這樣流經(jīng)電容的電流回路為:電源平面->過孔->引出線->焊盤->電容->焊盤->引出線->過孔->地平面,圖2直觀的顯示了電流的回流路徑。

第一種方法從焊盤引出很長的引出線然后連接過孔,這會(huì)引入很大的寄生電感,一定要避免這樣做,這是最糟糕的安裝方式。

第二種方法在焊盤的兩個(gè)端點(diǎn)緊鄰焊盤打孔,比第一種方法路面積小得多,寄生電感也較小,可以接受。

第三種在焊盤側(cè)面打孔,進(jìn)一步減小了回路面積,寄生電感比第二種更小,是比較好的方法。

第四種在焊盤兩側(cè)都打孔,和第三種方法相比,相當(dāng)于電容每一端都是通過過孔的并聯(lián)接入電源平面和地平面,比第三種寄生電感更小,只要空間允許,盡量用這種方法。

最后一種方法在焊盤上直接打孔,寄生電感最小,但是焊接是可能會(huì)出現(xiàn)問題,是否使用要看加工能力和方式。

推薦使用第三種和第四種方法。

需要強(qiáng)調(diào)一點(diǎn):有些工程師為了節(jié)省空間,有時(shí)讓多個(gè)電容使用公共過孔,任何情況下都不要這樣做。最好想辦法優(yōu)化電容組合的設(shè)計(jì),減少電容數(shù)量。

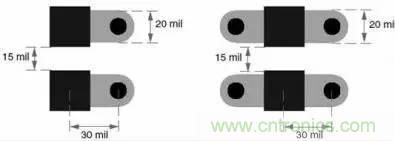

由于印制線越寬,電感越小,從焊盤到過孔的引出線盡量加寬,如果可能,盡量和焊盤寬度相同。這樣即使是0402封裝的電容,你也可以使用20mil寬的引出線。引出線和過孔安裝如圖4所示,注意圖中的各種尺寸。

推薦閱讀: