【導(dǎo)讀】基于I2C總線的圖像傳感器配置在視頻圖像采集處理系統(tǒng)中非常普遍,本設(shè)計(jì)結(jié)合了FPGA 的可編程特性�����,采用模塊化的方法設(shè)計(jì)方法完成了I2C 配置電路的設(shè)計(jì)�,詳細(xì)介紹了各個(gè)模塊的設(shè)計(jì)流程和實(shí)現(xiàn)方式,最后對(duì)整個(gè)設(shè)計(jì)進(jìn)行了仿真����,驗(yàn)證了設(shè)計(jì)的正確性�����。

基于FPGA 的嵌入式圖像檢測(cè)系統(tǒng)因其快速的處理能力和靈活的編程設(shè)計(jì)使得它在工業(yè)現(xiàn)場(chǎng)的應(yīng)用非常廣泛�,通常這些系統(tǒng)都是通過采集圖像數(shù)據(jù)流并對(duì)它實(shí)時(shí)處理得到所需的特征信息����。圖像數(shù)據(jù)的獲取是整個(gè)系統(tǒng)的第一步,作為整個(gè)系統(tǒng)的最前端���,它決定了原始數(shù)據(jù)的質(zhì)量����,是整個(gè)系統(tǒng)成功的關(guān)鍵���。CMOS 圖像傳感器采用CMOS 工藝�,可以將圖像采集單元和信號(hào)處理單元集成到同一塊芯片上��,因而在集成度���、功耗����、成本上具有很大優(yōu)勢(shì),這使得它在嵌入式圖像處理領(lǐng)域的運(yùn)用越來(lái)越多�����。CMOS 圖像傳感器芯片大都把 I2C 總線的一個(gè)子集作為控制接口��,用戶可以很方便地對(duì)芯片進(jìn)行編程操作����,根據(jù)設(shè)計(jì)要求的不同配置圖像傳感器內(nèi)部寄存器數(shù)據(jù)����,以獲取期望的圖像。

本文以Aptina 公司的MT9P031 圖像傳感器為例����,用Verilog 硬件描述語(yǔ)言設(shè)計(jì)了I2C 總線的接口電路,以FPGA 作為核心控制器實(shí)現(xiàn)了對(duì)MT9P031 初始化操作���,不僅驗(yàn)證了I2C 總線的配置效果���,得到了理想的圖像數(shù)據(jù),還為后續(xù)線結(jié)構(gòu)光圖像的處理系統(tǒng)奠定了基礎(chǔ)。

1 I2C 總線協(xié)議及MT9P031 配置過程介紹

1.1 I2C 總線協(xié)議

I2C(Inter-Integrated Circuit Bus) 總線是由PHILIPS 公司開發(fā)的兩線式用于芯片之間連接的總線�,由于其接口線少,控制方式簡(jiǎn)單�����,通信速率較高等特點(diǎn)��,在單片機(jī)��、串行EEPROM 等器件中有著廣泛的使用�����。I2C 總線用兩根信號(hào)線來(lái)進(jìn)行數(shù)據(jù)傳輸�,一根為串行數(shù)據(jù)(SDA, Serial Data),另一根為串行時(shí)鐘線(SCL, Serial Clock)���。若干兼容器件(如存儲(chǔ)器��、A/D���、D/A、LCD 驅(qū)動(dòng)器等)可以共享I2C 總線����。I2C 總線上所有器件依靠SDA 發(fā)送的地址信號(hào)尋址���,不需要片選線。任何時(shí)刻總線只能由一個(gè)主器件控制��,各從器件在總線空閑時(shí)啟動(dòng)數(shù)據(jù)傳輸�����。

1.2 MT9P031 配置時(shí)序分析

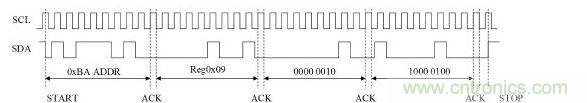

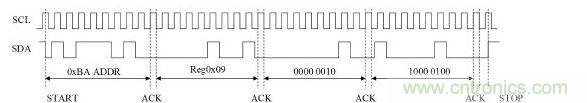

由于檢測(cè)系統(tǒng)需求的不同����,圖像傳感器可能要工作在不同的模式����,因此需要通過外部控制器對(duì)其內(nèi)部寄存器進(jìn)行讀寫操作,完成具體的配置���。典型的寫MT9P031 寄存器時(shí)序如圖1 所示���,起始信號(hào)過后,F(xiàn)PGA 先寫入設(shè)備(即MT9P031)的地址0xBA���,然后釋放SDATA 數(shù)據(jù)總線��,隨后MT9P031 返回一個(gè)應(yīng)答信號(hào)ACK��,F(xiàn)PGA 獲取應(yīng)答信號(hào)后��,經(jīng)過一個(gè)時(shí)鐘周期再傳送待配置的寄存器地址0x09����,在獲取應(yīng)答信號(hào)后再傳送16 位的寄存器數(shù)據(jù),由于每次只能發(fā)送8 位數(shù)據(jù)����,所以這16位的寄存器數(shù)據(jù)要分兩次才能發(fā)送完畢,先發(fā)送的是高八位數(shù)據(jù)�����,后發(fā)送的為低八位數(shù)據(jù)���,每發(fā)送完一個(gè)字節(jié)的數(shù)據(jù)���,F(xiàn)PGA均會(huì)獲取一位的應(yīng)答信號(hào),然后結(jié)束一個(gè)傳送周期�,完成一個(gè)寄存器的配置�,即IDAddress+ SUB-Address + W-Data 總共32位的數(shù)據(jù)���。重復(fù)上述過程可以對(duì)不同的寄存器進(jìn)行不同的參數(shù)配置��。

圖1 寫MT9P031 時(shí)序圖

2 FPGA 模塊設(shè)計(jì)

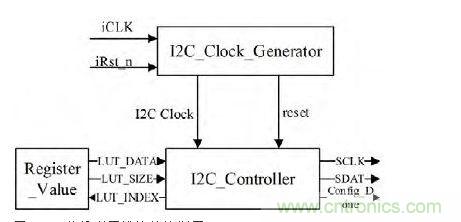

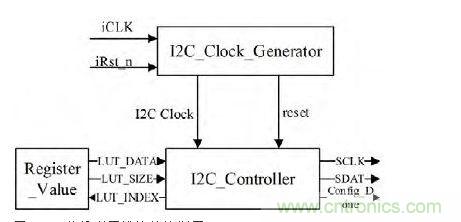

為了實(shí)現(xiàn)對(duì)圖像傳感器的正確配置�����,必須嚴(yán)格按照MT9P031 的配置時(shí)序完成設(shè)計(jì)���,本設(shè)計(jì)中I2C 總線配置模塊主要由三個(gè)小模塊構(gòu)成����,它們分別是I2C_Clock_Generator、I2C_Controller 和Register_Value�,各模塊之間的連接如圖2 所示。

圖2 I2C 總線配置模塊結(jié)構(gòu)框圖

I2C_Clock_Generator 主要產(chǎn)生負(fù)責(zé)產(chǎn)生I2C 串行時(shí)鐘信號(hào)���,根據(jù)協(xié)議數(shù)據(jù)傳輸有三種速度模式:正常模式100Kb/s�����、快速模式400Kb/s�����、高速模式3.4Mb/s�����,為了保證配置的準(zhǔn)確性和成功率�����,設(shè)計(jì)中采用了100Kb/ 的速度模式�,即SCLK 的頻率為100KHz,因?yàn)镕PGA 外部輸入的時(shí)鐘為50MHz���,所以需要對(duì)其分頻獲得��。同時(shí)該模塊還負(fù)責(zé)產(chǎn)生數(shù)據(jù)傳輸有效信號(hào)����,保證SDAT 的改變發(fā)生在SCLK 的低電平時(shí)段����。

Register_Value 其實(shí)一個(gè)查找表,負(fù)責(zé)保存MT9P031 內(nèi)部需要配置的寄存器地址和數(shù)據(jù)�����,查找表內(nèi)數(shù)據(jù)的位數(shù)都是24bit,單獨(dú)作為一個(gè)模塊的目的是為了方便用戶改變配置數(shù)據(jù)����,決定圖像傳感器的不同工作狀態(tài)。

I2C_Controller 是圖像傳感器配置設(shè)計(jì)的核心模塊���,主要完成了啟停命令產(chǎn)生�、字節(jié)發(fā)送和讀取���、應(yīng)答信號(hào)采集等功能��。同時(shí)���,I2C_Controller 模塊還產(chǎn)生I2C讀寫時(shí)序�,由狀態(tài)機(jī)嚴(yán)格按照I2C 協(xié)議實(shí)現(xiàn),將Register Value 部分送出的24 位操作碼I2C_DAT 轉(zhuǎn)化成為正確的I2C 時(shí)序���。一個(gè)寄存器的數(shù)據(jù)傳輸完成后���,模塊還將判斷寄存器配置數(shù)據(jù)是否發(fā)送順利��,如果一切正常�����,LUT_INDEX 信號(hào)會(huì)自動(dòng)加一����,控制Register Value 查找表產(chǎn)生下一個(gè)寄存器的地址和數(shù)據(jù)��。

3 I2C 接口的仿真及調(diào)試

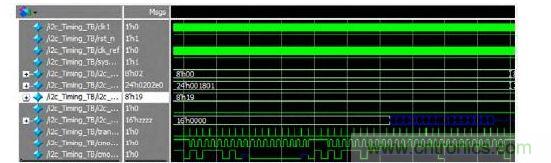

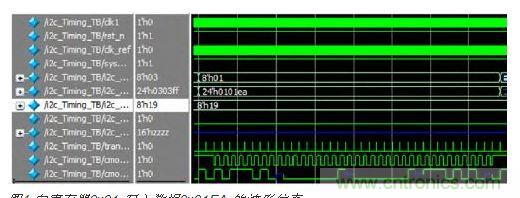

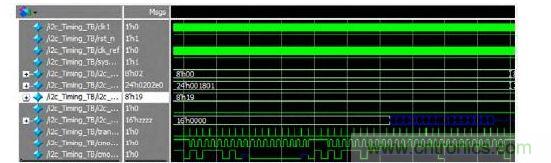

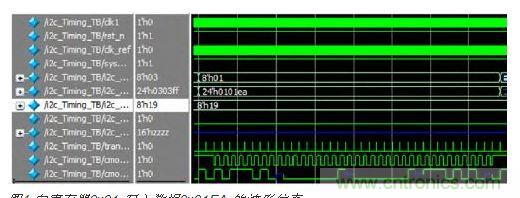

為了驗(yàn)證MT9P031 配置過程中I2C時(shí)序的正確性�,本設(shè)計(jì)在Modelsim Se10.1c 版軟件平臺(tái)中對(duì)整個(gè)模塊進(jìn)行了功能仿真,在Test bench 中模擬了50MHz 控制時(shí)鐘以及復(fù)位信號(hào)��,觀察最終輸出端的波形情況��。圖3 是對(duì)MT9P031 的寄存器地址0x00 進(jìn)行讀操作的仿真波形圖����,圖4是對(duì)寄存器地址0x01 寫入0x01EA 的仿真波形圖。

圖3 讀取寄存器0x00 的波形仿真

圖4 向寄存器0x01 寫入數(shù)據(jù)0x01EA 的波形仿真

4 總結(jié)

基于I2C總線的圖像傳感器配置在視頻圖像采集處理系統(tǒng)中非常普遍�����,本設(shè)計(jì)結(jié)合了FPGA 的可編程特性,采用模塊化的方法設(shè)計(jì)方法完成了I2C 配置電路的設(shè)計(jì)�����,詳細(xì)介紹了各個(gè)模塊的設(shè)計(jì)流程和實(shí)現(xiàn)方式�����,最后對(duì)整個(gè)設(shè)計(jì)進(jìn)行了仿真���,驗(yàn)證了設(shè)計(jì)的正確性�����。綜合調(diào)試后占用資源極小����,可靠性高���,而且利用Verilog 硬件描述語(yǔ)言的設(shè)計(jì)使得可移植性很強(qiáng)�,具有廣泛的應(yīng)用價(jià)值�。