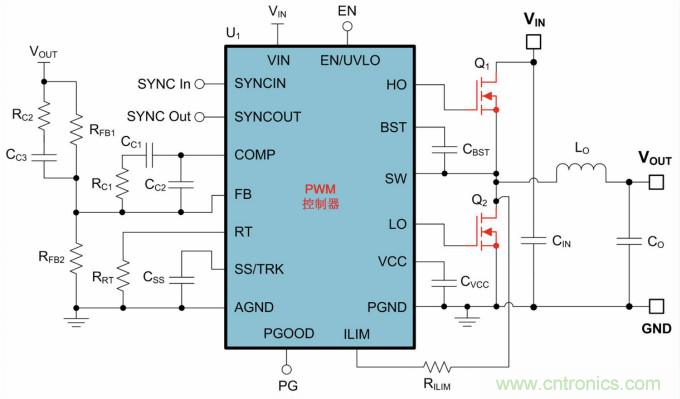

【導(dǎo)讀】本系列文章的第 1 部分至第 5 部分中,介紹了抑制傳導(dǎo)和輻射電磁干擾 (EMI) 的實(shí)用指南和示例,尤其是針對(duì)采用單片集成功率 MOSFET 的 DC/DC 轉(zhuǎn)換器解決方案進(jìn)行了詳細(xì)介紹。在此基礎(chǔ)上,本文繼續(xù)探討使用控制器驅(qū)動(dòng)分立式高、低側(cè)功率 MOSFET 對(duì)的 DC/DC 穩(wěn)壓器電路適用的 EMI 的抑制技術(shù)。使用控制器(例如圖 1 所示同步降壓穩(wěn)壓器電路中的控制器)的實(shí)現(xiàn)方案具有諸多優(yōu)點(diǎn),包括能夠增強(qiáng)電流性能,改善散熱性能,以及提高設(shè)計(jì)選擇、元器件選型和所實(shí)現(xiàn)功能的靈活性。

圖 1:驅(qū)動(dòng)功率 MOSFET Q1 和 Q2 的同步降壓控制器的原理圖

然而,從 EMI 角度來看,采用分立式 FET 的控制器解決方案與采用集成 FET 的轉(zhuǎn)換器相比,更具挑戰(zhàn)性。主要有兩方面的考量因素。首先,在緊湊性方面,采用 MOSFET 和控制器的功率級(jí)的印刷電路板 (PCB) 布局比不上采用優(yōu)化引腳布局和內(nèi)部柵極驅(qū)動(dòng)器的功率轉(zhuǎn)換器集成電路 (IC) 。其次,對(duì)于死區(qū)時(shí)間管理,在 MOSFET 開關(guān)時(shí)間在額定范圍的轉(zhuǎn)換器中通常更精確。因此,體二極管導(dǎo)通時(shí)間更短,從而能夠改善開關(guān)性能并降低與反向恢復(fù)相關(guān)的噪聲。

本文提供與采用 MOSFET 和控制器及半橋設(shè)計(jì)的多層 PCB 相關(guān)指南,以實(shí)現(xiàn)出色的 EMI 性能。當(dāng)務(wù)之急是謹(jǐn)慎選擇功率級(jí)元器件和適合的 PCB 布局,最大程度地減小關(guān)鍵回路寄生電感。布局示例表明,可以在不犧牲效率或熱性能指標(biāo)的情況下減少傳導(dǎo)電磁輻射。

迎接 EMI 相關(guān)挑戰(zhàn)

產(chǎn)生 EMI 的三個(gè)基本要素包括:電噪聲源、耦合路徑及受擾接收器。應(yīng)對(duì)其中一個(gè)或所有基本要素,可以實(shí)現(xiàn)干擾抑制,從而實(shí)現(xiàn)合電磁兼容性 (EMC)。在實(shí)踐中,可以采用多種技術(shù)中斷耦合路徑和/或強(qiáng)化可能的受擾電路,例如插入 EMI 濾波器來抑制傳導(dǎo)干擾,借助屏蔽來降低輻射干擾等。

對(duì)于與降壓穩(wěn)壓器的不連續(xù)輸入電流(或升壓穩(wěn)壓器的不連續(xù)輸出電流)相關(guān)的低頻 EMI 頻譜幅值,采用傳統(tǒng)的濾波器級(jí)進(jìn)行處理相對(duì)容易。然而,與開關(guān)換向期間電壓和電流的尖銳邊緣相關(guān)的高 dv/dt 以及 di/dt 會(huì)產(chǎn)生諧波分量,從而導(dǎo)致出現(xiàn)更大的問題。高電流柵極驅(qū)動(dòng)器(在電壓低于 100V 時(shí),通常集成在控制器中)可以以極高的速度開關(guān)功率 MOSFET。傳統(tǒng)硅 FET 的轉(zhuǎn)換率通常大于 10V/ns和 1A/ns,基于氮化鎵 (GaN) 的器件轉(zhuǎn)換率可能更高。我對(duì)本文第 2 部分中梯形開關(guān)波形的時(shí)域特性與其頻譜成分之間的關(guān)系進(jìn)行了研究,闡述了波形的最陡斜率決定高頻頻譜的漸近包絡(luò),因此,采用降低 dv/dt 和 di/dt 的方法有助于降低產(chǎn)生 EMI 的可能性。

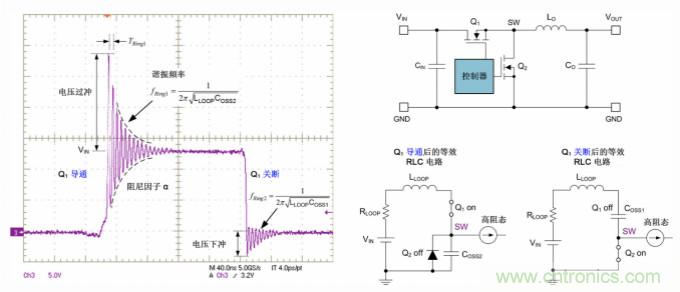

除了電壓和電流的尖銳邊沿之外,與開關(guān)波形相關(guān)的過沖/下沖及隨后產(chǎn)生的振鈴也非常棘手。圖 2 顯示了硬開關(guān)同步降壓穩(wěn)壓器的開關(guān)節(jié)點(diǎn)電壓波形。開關(guān)節(jié)點(diǎn)電壓振鈴頻率范圍為 50MHz 至 250MHz,具體取決于寄生功率回路電感的諧振 (LLOOP)及 MOSFET 輸出電容 (COSS)。此類高頻分量可以通過近場(chǎng)耦合傳播到輸出總線、周邊元器件或輸入電源線,并且難以通過傳統(tǒng)濾波衰減。同步 MOSFET 體二極管反向恢復(fù)存在類似的負(fù)面作用,當(dāng)二極管恢復(fù)電流流入寄生回路電感時(shí),振鈴電壓升高。

圖 2:同步降壓穩(wěn)壓器在 MOSFET 導(dǎo)通和關(guān)斷轉(zhuǎn)換期間的開關(guān)節(jié)點(diǎn)電壓波形和等效電路

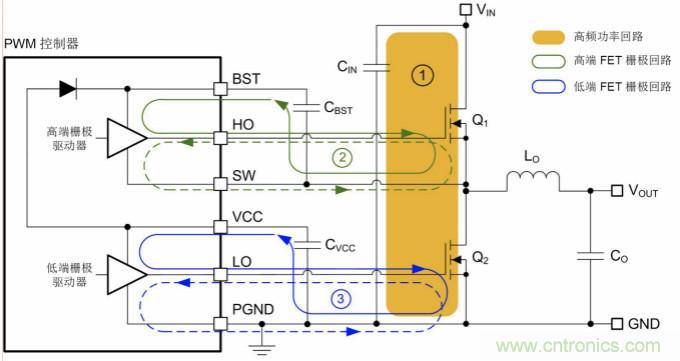

圖 3 的原理圖標(biāo)出了降壓調(diào)節(jié)器電路 [6] 的關(guān)鍵高頻功率回路,代表了具有高轉(zhuǎn)換率電流的電路元件。可以對(duì)升壓、反相降壓-升壓、單端初級(jí)側(cè)電感轉(zhuǎn)換器 (SEPIC) 和其他拓?fù)溥M(jìn)行類似檢查。最大限度縮減功率回路的面積至關(guān)重要,原因是該參數(shù)與寄生電感和相關(guān) H 場(chǎng)傳播成正比。主要設(shè)計(jì)目標(biāo)是通過減小寄生電感最大程度提升寄生 LC 諧振電路的諧振頻率。由此,降低存儲(chǔ)的無功能量總值,減少開關(guān)節(jié)點(diǎn)電壓峰值過沖和振鈴。此外,達(dá)到臨界阻尼因子的等效電阻實(shí)際上更低,因此任何振鈴都會(huì)更早衰減 - 在高頻時(shí)的趨膚效應(yīng)增大回路的寄生電阻時(shí)更是如此。

圖 3:標(biāo)出了同步降壓穩(wěn)壓器中對(duì) EMI 至關(guān)重要的高頻電流回路

圖 3 中,還顯示了導(dǎo)通和關(guān)斷期間高側(cè)和低側(cè) MOSFET 的柵極驅(qū)動(dòng)器回路。務(wù)必遵從功率級(jí)布局期間的特殊注意事項(xiàng)(下文討論),確保功率回路、柵極回路和共源寄生電感都盡可能低。

實(shí)現(xiàn)低 EMI 的 PCB 布局設(shè)計(jì)

以下步驟總結(jié)了 DC/DC 穩(wěn)壓器中元器件位置和 PCB 布局的基本準(zhǔn)則,以幫助盡可能降低噪聲和 EMI 信號(hào)。其中一些步驟類似于第 5 部分中針對(duì)采用集成 MOSFET 的基于轉(zhuǎn)換器的設(shè)計(jì)所介紹的步驟。在后續(xù)部分,我將提供 PCB 布局案例研究,探討如何優(yōu)化降壓穩(wěn)壓器 EMI 特性。

● 布線及元器件排布

● 將所有功率級(jí)元器件排布在 PCB 頂部。

— 避免將開關(guān)節(jié)點(diǎn)覆銅和電感放在底部,以免對(duì) EMI 測(cè)試裝置的基準(zhǔn)平面產(chǎn)生輻射。

● 將 VCC 或 BIAS 的旁路電容放置于靠近各自引腳的位置。

— 在將 AGND 引腳與 GND 相連之前,首先電路中連入 CVCC 和 CBIAS 電容。

● 將臨近的自舉電容與控制器的 BOOT 和 SW 引腳相連接。

— 利用鄰近的接地覆銅屏蔽 CBST 電容和開關(guān)節(jié)點(diǎn),降低共模噪聲。

● GND 平面設(shè)計(jì)

● 將 PCB 分層板中的第 2 層接地平面盡可能放在靠近頂層功率級(jí)元器件的位置,以消除 H 場(chǎng)、降低寄生電感及屏蔽噪聲。

● 使用位于頂層與第二層接地平面之間的低 z 軸間距獲得最佳映像平面效果。

— 在 PCB 分層規(guī)范中將層間距指定為 6 mil。

● 輸入和輸出電容

● 放置降壓穩(wěn)壓器的 CIN,盡量減小將 CIN 連接到功率 MOSFET 所形成的回路面積。對(duì)于升壓穩(wěn)壓器和 SEPIC 穩(wěn)壓器的 COUT,同樣建議如此操作。

— 功率回路分類為橫向或縱向,具體取決于電容相對(duì)于 MOSFET 的放置位置。

● CIN 和 COUT 的接地返回路徑應(yīng)由集中放置的頂層平面組成。

— 使用多個(gè)外部或內(nèi)部 GND 平面連接 DC 電流路徑。

● 使用外殼尺寸為 0402 或 0603 的低等效串聯(lián)電感 (ESL) 陶瓷電容,并放在 MOSFET 附近,以最大限度地減小功率回路寄生電感。

● 電感和開關(guān)節(jié)點(diǎn)布局

● 將電感放置在靠近 MOSFET 的位置。

— 盡量減小開關(guān)節(jié)點(diǎn)覆銅多邊形面積,從而盡量避免電容耦合及減小共模電流。覆銅區(qū)應(yīng)僅覆蓋電感焊盤并僅占用連接 MOSFET 端子所需的最小面積。

● 使用鄰近的接地保護(hù)并通過屏蔽限制開關(guān)節(jié)點(diǎn)噪聲。

● 檢查電感點(diǎn)位置,確保與開關(guān)節(jié)點(diǎn)相連的繞組末端位于繞組幾何結(jié)構(gòu)內(nèi)部的底部,由連接到 VOUT(降壓穩(wěn)壓器)或 VIN(升壓穩(wěn)壓器)的繞組的外層繞線提供屏蔽。

● 選擇在封裝下方設(shè)有端子的電感。

— 避免使用可能產(chǎn)生天線輻射效應(yīng)的大型側(cè)壁式端子。

● 盡可能使用電場(chǎng)屏蔽電感。將屏蔽端子與 PCB 接地平面相連。

● 柵極驅(qū)動(dòng)器布線

● 將控制器放置在盡可能靠近功率 MOSFET 的位置。

— 連接 HO 和 SW 的柵極驅(qū)動(dòng)器時(shí),應(yīng)分別采用最小的布線長度和最小的回路面積,直接連接到高側(cè) MOSFET 柵極和源極端子。

— 將 LO 的柵極驅(qū)動(dòng)器直接連接到接地平面上方的低側(cè) MOSFET 柵極,并盡量減小介電間距。

— 對(duì)柵極驅(qū)動(dòng)器進(jìn)行正交布線,盡量減少功率回路與柵極回路之間的耦合。

● EMI 管理

● 連接 EMI 濾波器元器件時(shí),應(yīng)避免由電感和開關(guān)節(jié)點(diǎn)輻射產(chǎn)生的電場(chǎng)形成耦合。

— 如果 EMI 濾波器與功率級(jí)的分隔距離不足,可將 EMI 濾波器放在電路板上轉(zhuǎn)換器的對(duì)側(cè)。

● 在 EMI 濾波器下方的所有層上開口,以防寄生耦合路徑影響濾波器的衰減特性。

● 根據(jù)需要,可添加一個(gè)與 CBOOT 串聯(lián)的電阻(最好小于 10Ω),限制 MOSFET 導(dǎo)通速度,從而降低開關(guān)節(jié)點(diǎn)電壓轉(zhuǎn)換率,減少過沖和振鈴。

— 自舉電阻會(huì)改變驅(qū)動(dòng)電流瞬變率,從而降低 MOSFET 導(dǎo)通期間的開關(guān)節(jié)點(diǎn)電壓和電流轉(zhuǎn)換率。

— 為提高靈活性,可以考慮使用具有柵極驅(qū)動(dòng)器專用源極引腳和漏極引腳的控制器。

● 任何所需的開關(guān)節(jié)點(diǎn)緩沖電路都應(yīng)根據(jù)每次開關(guān)轉(zhuǎn)換時(shí)的瞬態(tài)電流峰值,占用最小的回路面積。

— 將封裝尺寸最小的元器件連接到 SW(通常是電容),盡量降低其天線效應(yīng)。

● 使用具有內(nèi)部接地平面的多層 PCB,與雙層設(shè)計(jì)相比,其性能得到顯著提升。

— 避免阻斷 MOSFET 附近的高頻電流路徑。

● 考慮采用金屬外殼屏蔽優(yōu)化輻射 EMI 性能。

— 屏蔽外殼可覆蓋除 EMI 濾波器之外的所有功率級(jí)元器件,外殼與 PCB 上的 GND 相連,基本形成了一個(gè)帶有 PCB 接地平面的法拉第籠。

DC/DC 同步降壓控制器案例研究

圖 4 顯示用于汽車應(yīng)用或噪聲敏感型工業(yè)應(yīng)用的同步降壓轉(zhuǎn)換器電路 [6] 的原理圖。其中融合了有助于改善 EMI 性能的多項(xiàng)特性,包括恒定開關(guān)頻率操作、外部時(shí)鐘同步以及通過高側(cè) MOSFET 受控導(dǎo)通實(shí)現(xiàn)的開關(guān)節(jié)點(diǎn)整形(轉(zhuǎn)換率控制)。為了幫助實(shí)現(xiàn)最佳的 PCB 布局,原理圖中將高電流走線(VIN、PGND、SW 連接)、噪聲敏感型網(wǎng)絡(luò)(FB、COMP、ILIM)和高 dv/dt 電路節(jié)點(diǎn)(SW、BST、HO、LO、SYNC)突出顯示。高 di/dt 回路類似于圖 3 中標(biāo)示的回路。

圖 4:DC/DC 降壓穩(wěn)壓器原理圖,其中標(biāo)示出 PCB 布局的重要節(jié)點(diǎn)和走線

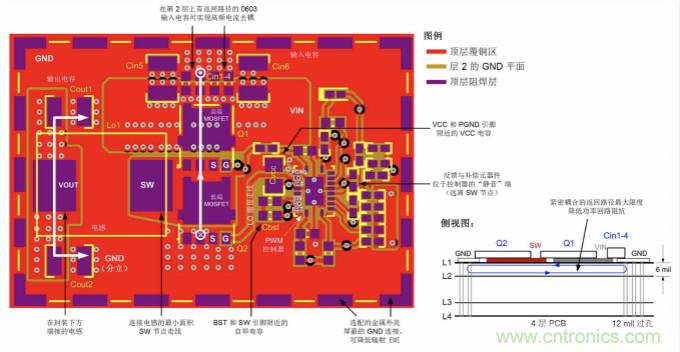

圖 5 顯示了功率 MOSFET 及輸入電容的兩種橫向回路布局。功率級(jí)位于 PCB 頂層,控制器放置于底部。橫向回路設(shè)計(jì)在頂層存在循環(huán)電流(圖 5 中用白框表示),該電流在第二層接地平面上感應(yīng)出映像電流,以抵消磁通,從而降低寄生回路電感。

更具體來說,修改圖 5b 中的布局,使高側(cè) FET (Q1) 旋轉(zhuǎn) 90 度。這樣可以改善 Q1 的散熱效果,從而更好地進(jìn)行熱管理,并可以在 MOSFET 附近方便地放置外殼尺寸為 0603 的低 ESL 電容 (Cin1),以實(shí)現(xiàn)高頻去耦??紤]到功率級(jí)元器件的 U 型布局方向,較短返回連接的輸出電容將放置在低側(cè) MOSFET。

圖 5:兩種傳統(tǒng)的橫向回路布局設(shè)計(jì)

改進(jìn)后的 PCB 布局設(shè)計(jì)

圖 6 所示為改進(jìn)后的布局,其優(yōu)勢(shì)是可減小功率回路面積,使多層結(jié)構(gòu)達(dá)到高效率。該設(shè)計(jì)將 PCB 的第 2 層用作功率回路返回路徑。該返回路徑位于頂層的緊下方,形成小尺寸物理回路。垂直回路中的反向電流可使磁場(chǎng)自行消除,從而進(jìn)一步減小寄生電感。圖 6 中的側(cè)視圖展示了在多層 PCB 結(jié)構(gòu)中形成小尺寸自行消除回路的概念。

將四個(gè) 0603 輸入電容放置在盡可能接近高側(cè) MOSFET 的位置(位于圖 6 中大容量輸入去耦電容 CIN1 與 CIN2 之間),這四個(gè)電容具有較小的 0402 或 0603 外殼尺寸及較低的 ESL。這些電容的返回連接通過多個(gè) 12 mil 的過孔連接到第 2 層接地平面。第 2 層接地平面在 MOSFET 的緊下方提供了至低側(cè) MOSFET 源極端子的電流返回路徑。

圖 6:采用垂直功率回路設(shè)計(jì)的功率級(jí)和控制器的布局

此外,開關(guān)節(jié)點(diǎn)覆銅多邊形區(qū)域只包含電感焊盤以及連接 MOSFET 所需的最小面積。接地平面覆銅區(qū)可屏蔽將 MOSFET 連接到電感端子的多邊形覆銅區(qū)。SW 和 BST 的單層布局意味著 PCB 的底側(cè)不會(huì)有 dv/dt 較高的過孔。這樣可以避免在 EMI 測(cè)試期間,電場(chǎng)與基準(zhǔn)接地平面耦合。最后,在電感兩側(cè)各使用一個(gè)陶瓷輸出電容 COUT1 和 COUT2,優(yōu)化輸出電流回路。在輸出端引出兩個(gè)并聯(lián)的返回路徑可以將返回電流分成兩部分,有助于減弱“地彈反射”效應(yīng)。

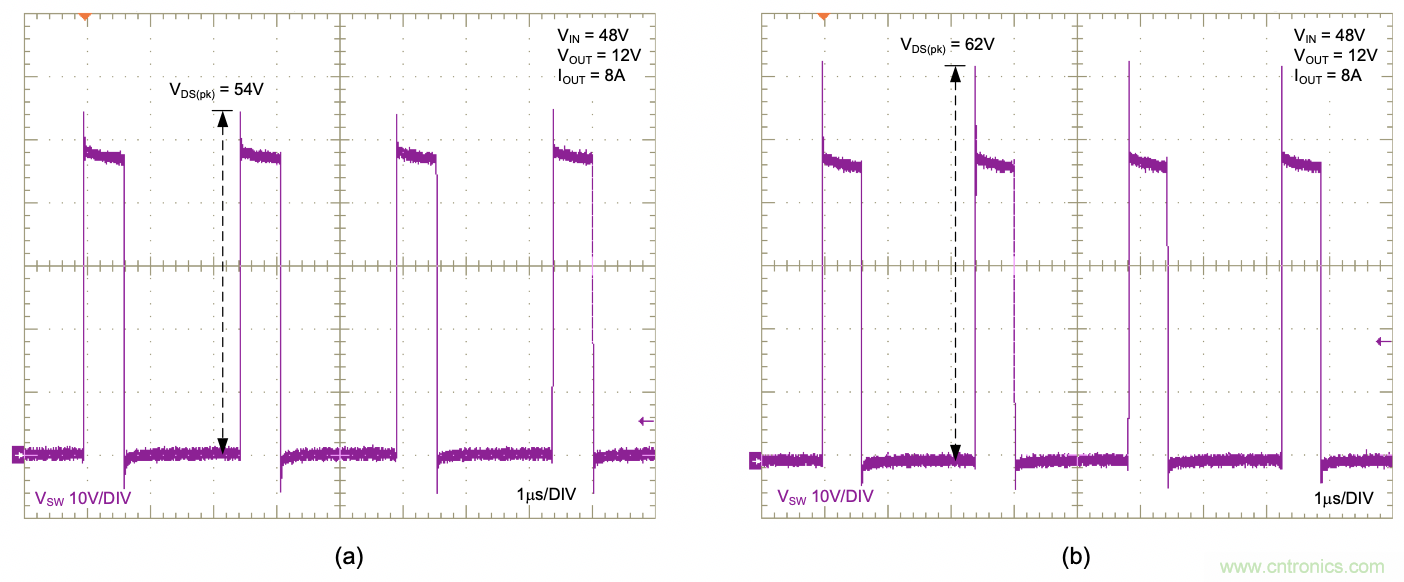

圖 7a 所示為,圖 4 中的穩(wěn)壓器采用圖 6 中的優(yōu)化布局時(shí),使用寬帶探頭測(cè)得的開關(guān)節(jié)點(diǎn)電壓波形。振鈴不明顯,只存在低幅度過沖和下沖,表示 50MHz 以上時(shí) EMI 性能良好。為進(jìn)行對(duì)比,圖 7b 顯示了采用圖 5b 所示橫向回路布局的類似測(cè)量結(jié)果。優(yōu)化布局的峰值過沖降低約 8V。

圖 7:VIN = 48V,IOUT = 8A 時(shí)的開關(guān)節(jié)點(diǎn)電壓波形,(a) 為優(yōu)化布局,(b) 為橫向回路布局

圖 8 所示為圖 6 中的轉(zhuǎn)換器在 150kHz 至 108MHz 下測(cè)得的傳導(dǎo)發(fā)射。使用 Rohde & Schwarz 的頻譜分析儀,所得檢測(cè)器掃描結(jié)果的峰值和平均值分別以黃色和藍(lán)色表示。結(jié)果符合國際無線電干擾特別委員會(huì) (CISPR) 25 5 類要求。紅色限值圖象為 5 類峰值和平均值限值(峰值限值通常比平均值限值高出 20dB)。

圖 8:CISPR 25 傳導(dǎo)發(fā)射測(cè)量結(jié)果,(a) 頻率范圍為 150kHz 至 30MHz,(b) 頻率范圍為 30MHz 至 108MHz

總結(jié)

功率半導(dǎo)體器件的開關(guān)瞬變是傳導(dǎo) EMI 和輻射 EMI 的主要來源。本文重點(diǎn)介紹在使用控制器和外部 MOSFET 的 DC/DC 穩(wěn)壓器電路中,有助于降低 EMI 的 PCB 布局。關(guān)于布局的主要建議包括,盡量減小布局中的電流“熱回路”面積,避免阻斷電流路徑,采用具有內(nèi)部接地平面的多層 PCB 結(jié)構(gòu)實(shí)現(xiàn)屏蔽(性能遠(yuǎn)超雙層 PCB),以差分對(duì)形式敷設(shè)短而直接的柵極驅(qū)動(dòng)器走線,以及通過盡量減小開關(guān)節(jié)點(diǎn)覆銅區(qū)域面積來降低電場(chǎng)輻射耦合。

優(yōu)化后的 PCB 布局有助于改善穩(wěn)壓器的 EMI 信號(hào)(與降低 EMI 的其他常用“修復(fù)”手段不同,不會(huì)犧牲效率或熱性能)。盡管本文圍繞 EMI 敏感的同步降壓功率級(jí)進(jìn)行論述,但只要能確定關(guān)鍵回路并實(shí)施文中建議采用的布局方法,通??梢詫⑦@些概念推廣至任何 DC/DC 穩(wěn)壓器。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請(qǐng)聯(lián)系小編進(jìn)行處理。

推薦閱讀: