【導讀】一般而言,在高輸出電流隔離式DC-DC電源應用中,使用 同步整流器(尤其是MOSFET)是主流趨勢。高輸出電流還 會在整流器上引入較高的di/dt。為了實現(xiàn)高效率,MOSFET 的選擇主要取決于導通電阻和柵極電荷。

一般而言,在高輸出電流隔離式DC-DC電源應用中,使用 同步整流器(尤其是MOSFET)是主流趨勢。高輸出電流還 會在整流器上引入較高的di/dt。為了實現(xiàn)高效率,MOSFET 的選擇主要取決于導通電阻和柵極電荷。然而,人們很少 注意寄生體二極管反向恢復電荷(Qrr)和輸出電容(COSS)。這 些關鍵參數(shù)可能會增大MOSFET漏極上的電壓尖峰和振鈴。 一般而言,隨著MOSFET擊穿電壓額定值的增大,導通電阻 也會增大。本文提出一種數(shù)控有源鉗位吸收器。該吸收器 既可消除同步整流器上的電壓尖峰和振鈴,還能發(fā)揮設計 指南作用;在隔離式DC-DC轉換器(如半橋和全橋拓撲結 構)中擁有多種其他優(yōu)勢,同時還能提高可靠性,降低故 障率。

簡介

人們總是希望使用平均故障間隔時間(MTBF)較高的高可靠性電 源。要打造穩(wěn)健的設計,可以使用額定擊穿電壓較高的開關。 但這樣做會喪失一定的效率。因此,高效率和高可靠性在實際應用中往往不可兼得。作為新一代電源解決方案的一部分,工 業(yè)界一直對高效率隔離式DC-DC轉換器保持著穩(wěn)定的需求。這 就要求在副邊使用同步整流器。整流器的額定值一般是器件電 壓尖峰的1.2至1.5倍。電壓尖峰由漏感、寄生走線電感和整流 器輸出電容(COSS)形成的諧振所導致,諧振峰值可能高達整流器 穩(wěn)態(tài)反向電壓的兩倍。一種解決方案是用無源吸收器充當RC1或 RCD2。雖然這些器件非常流行,但有損耗,會導致效率略微下 降。用于制造無損吸收器的部分技術采用的是再生吸收器(如 LCD3),但吸收器僅用于原邊開關,或者只在電源開關關閉而 非開啟期間使用RC吸收器。其他技術4,5運用泄漏電能來驅動小 型高效率轉換器,饋入輸出電壓終端。但這要求使用更多的元 件。其他技術6則將有源鉗位吸收器用于全橋相移拓撲結構,以 便消除在ZVS軟開關應用中由原邊諧振電感導致的諧振,但僅 限于低占空比應用。

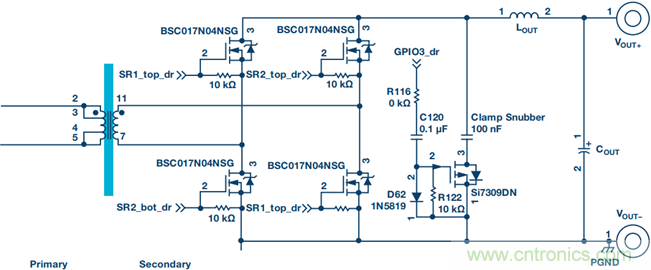

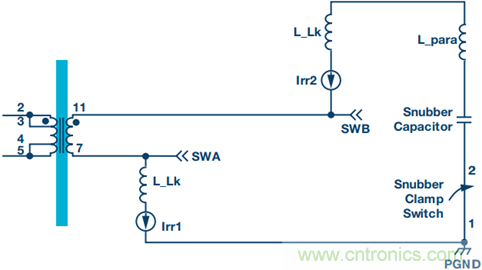

本文將深入探討有源鉗位吸收器電路及其數(shù)字實現(xiàn)方式,該吸 收器電路可以避免電壓偏移,特別是能消除MOSFET中寄生二極 管的反向恢復損耗,還具有多種其他優(yōu)勢。轉換器(僅副邊) 功率級示意圖如圖1所示。

圖1. 功率轉換器副邊(圖中所示為有源鉗位)

圖1展示的是一款隔離式DC-DC轉換器的副邊。副邊由同步整流 構成,同步整流表現(xiàn)為連接變壓器的H-橋。另外還有輸出濾波 器電感(LOUT)和輸出濾波器電容(COUT)。有源鉗位開關是一個P溝道 MOSFET,用于轉換柵極信號電平的柵極驅動由一個電容和一個 二極管構成。

高頻等效電路

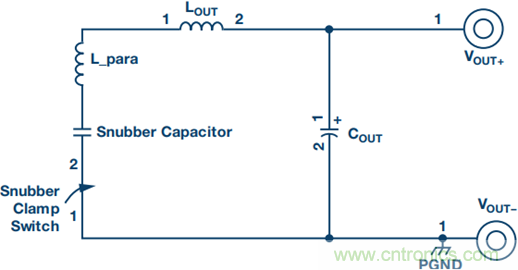

在高頻視圖中,大電感和大電容分別處于開路和短路狀態(tài),電 路分析中只使用寄生和諧振電感及電容。利用這種方法可以簡 化電路,以便分析交流電流。該方法特別適用于諧振拓撲結構 和使用吸收器的場合,因為在緩沖周期中,高頻電流會選擇阻 抗最低的路徑。

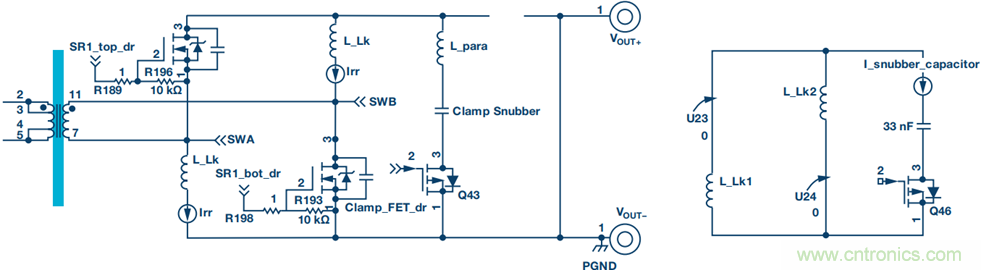

電路的交流視圖如圖2所示。輸出濾波電感和電容分別處于開 路和短路狀態(tài)。在電路中,MOSFET的輸出電容和漏電電感保持 原樣。重點是轉換器的副邊,因為原邊電壓源已短路并且對分 析無用。

圖2. (左)功率轉換器副邊AC視圖(圖中所示為有源鉗位)(右)簡化的AC視圖。

同步FET有源鉗位電路的工作原理

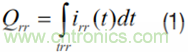

在分析中,我們假設,吸收器電容足夠大,能維持電壓恒定不 變。在續(xù)流間隙(在圖3中,SR1和SR2均開啟),四個副邊開 關(MOSFET)全部開啟。受有限上升和下降時間以及柵極驅動信 號傳播延遲變化的影響,同步整流器信號之間始終存在較短的 死區(qū)時間。在該死區(qū)時間期間,MOSFET的寄生二極管會導通以 續(xù)流。其后是下一半開關周期,此時,原邊MOSFET的另一個引 腳啟動。這會導致變壓器繞組上的極性發(fā)生變化,同時關閉同 步整流器體二極管。然而,只要反向恢復電荷(Qrr)未耗盡,同 步MOSFET的寄生二極管就不會關閉。方向如圖2所示。該Qrr被 視為作為前沿尖峰從變壓器反映到原邊的多余電流。這還會增 大同步MOSFET漏極上的電壓尖峰。反向恢復電荷的大小由下式 計算得到:

圖3

圖4a. trr間隔捕獲反向恢復能量期間的工作情況

圖4b. 負載中釋放的能量

漏電電感和走線電感(極性如圖2所示)導致的電壓尖峰由有 源鉗位吸收器吸收。有源吸收器開關可以在寄生二極管開啟后 在ZVS時打開。然而,當有源鉗位吸收器開啟時,吸收器電容會 吸收反向恢復電流并把捕獲的能量重新注入副橋和負載中。由 于通過吸收器電容的凈電流為零,所以只要轉換器工作于穩(wěn)態(tài) 下,吸收器就會維持電荷平衡。

設計指南

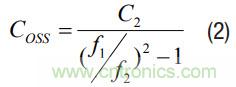

1. 估算漏電電感

讓轉換器在無吸收器的條件下工作,測量同步MOSFET漏極上振 鈴電壓尖峰的諧振頻率和周期(f1)。另外,測量原邊電流波形上 的前沿尖峰(應等于trr)。要估算漏電電感,要使電容的已知 值(C2)至少比MOSFET漏極/源極電容大一個數(shù)量級。用下式測量 振鈴頻率(f2),計算電容(COSS)和漏電(LLK)電感:

2. 選擇有源鉗位吸收器電容

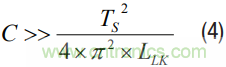

選擇一個輸出電容至少為同步MOSFET輸出電容10至100倍的吸 收器電容。這是因為有源吸收器開關會有一條低阻抗路徑。然 而,吸收器電容的選擇必須做到:

其中,Ts為開關周期。

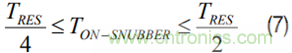

在下列最小延遲條件下打開有源鉗位吸收器:

這兩項為驅動器的傳播延遲和原邊MOSFET的驅動信號上升時 間。這個時序非常重要,因為必須捕獲MOSFET體二極管的全部 反向恢復能量。該時間取決于同步MOSFET體二極管的反向恢復 特性(Qrr、trr、Irr),可能隨器件上的溫度、負載電流和反向電 壓等因素而變化。延遲時間和吸收器導通時間可以用本文所述 方法精確設置以針對不同的開關特性進行優(yōu)化。

確定鉗位電容值的另一種方法是使用以下公式。該公式基于諧 振周期,在此期間,將漏電電能釋放到鉗位電容中。

該值的范圍為:

為了避免在第1點上觀察到過多的振鈴,導通時間應不超過一個 或兩個諧振周期,否則,會出現(xiàn)過多的連續(xù)振鈴?;蛘撸?器的導通時間可以取上面第1點中觀察到的前沿尖峰的導通時間 的近似值(如trr)。過多的導通時間只是會導致能量再諧振幾 個周期,可以在原邊電流波形中看到這一點(圖8和圖9)。

3. 選擇吸收器開關

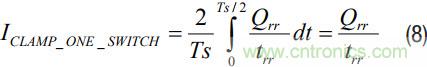

(1)的一個簡化版本是使用MOSFET數(shù)據(jù)手冊中的最差條件限值。 以下公式更加詳細地展現(xiàn)了電容中電流的情況:

使用因子2是因為考慮的只是半個開關周期,對于全橋或半橋 拓撲結構,該過程發(fā)生兩次。另外,在圖1中,由于兩個開關 關閉,所以反向恢復電荷會增加一倍。因此,總電流為:

其中,在全橋配置下,C為2;在中心抽頭配置下,C為1;N為 并聯(lián)的MOSFET數(shù)目。這是通過有源吸收器開關的平均電流。

數(shù)字實現(xiàn)

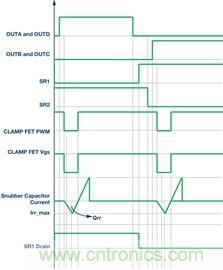

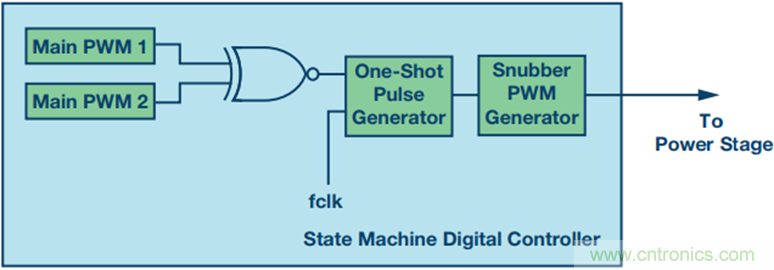

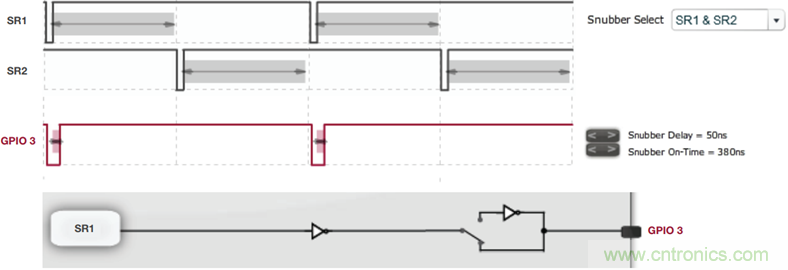

有源鉗位吸收器的數(shù)字實現(xiàn)有兩個控制:控制1是吸收器延 遲(自觸發(fā)器邊沿的吸收器PWM邊沿中的可調延遲)。控制2 為吸收器PWM導通時間。觸發(fā)點為H橋對邊引腳原邊PWM上升 沿的邏輯OR(如OUTC和OUTD)。吸收器PWM并不要求像主控 PWM分辨率一樣高的分辨率(如125 ps)。結果,觸發(fā)所需時 鐘能支持較慢的速率(5 ns分辨率),這樣還能節(jié)能(40倍系 數(shù))。這一概念也可以運用到副邊上有中心抽頭的功率轉換拓 撲結構。另外,該概念也可以用于單個開關,在這些開關中, 每個功率晶體管上會放置一個分立式有源鉗位開關吸收器單 元。在這種情況下,有源鉗位FET的驅動信號取自同步整流器 的下降沿。

圖5. 吸收器PWM的數(shù)字實現(xiàn)

ADP1055數(shù)字控制器提供了實現(xiàn)這一目標的必要工具。借助直觀 簡單的圖形用戶界面,只需幾分鐘就能完成有源鉗位吸收器的 優(yōu)化。ADP1055提供了兩個選項來設置吸收器PWM,即通過SR1 和SR2的邏輯組合或通過OUTC和OUTD信號的邏輯組合。在兩種 情況下,可以用兩個選項配置吸收器PWM,如圖6和圖7所示。 在上述所有情景下,都可以用吸收器延遲(設置死區(qū)時間)和 吸收器導通時間微調優(yōu)化參數(shù)。借助兩個信號的邏輯組合和極 性選擇功能,用戶完全可以自由地選擇適當?shù)奈掌鹘M合。

圖6. 使用選項1(SR1和SR2)的吸收器時序

圖7. 使用選項2(OUTC和OUTD)的吸收器時序

全橋拓撲結構的實驗結果

為了進行實驗驗證,選擇的隔離式DC-DC轉換器,其額定輸入 為48 V,額定輸出為12 V、20 A,開關頻率為125 kHz。拓撲結構 為全橋,帶一個副邊,如圖1所示。

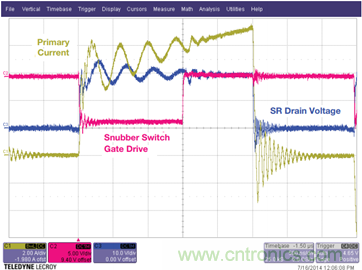

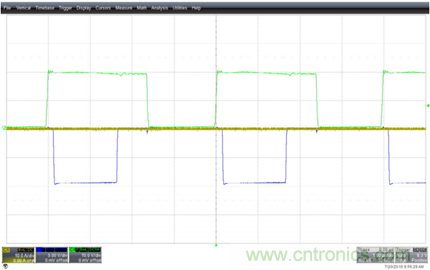

圖8展示了使用不正確的吸收器導通時間會導致多余振鈴,同時 還展示了同步MOSFET的振蕩漏極電壓,后者也反映在原邊電流 中。前沿尖峰也很嚴重,會導致不必要的EMI。

圖8. 過多的吸收器導通時間

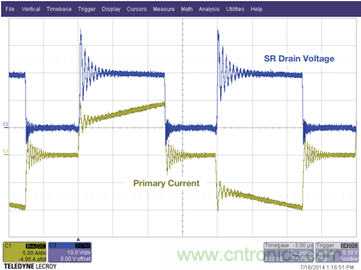

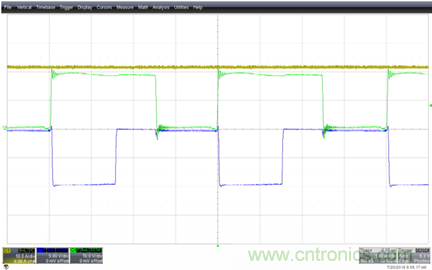

圖9所示為優(yōu)化的吸收器導通時間,其中,在同步MOSFET的漏 極電壓上無振鈴。同時,前沿尖峰也幾乎消除了。

圖9. 優(yōu)化的吸收器時序

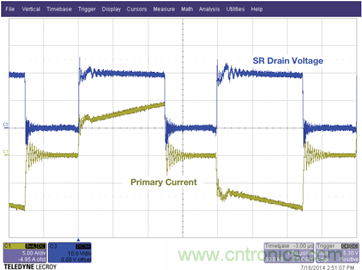

圖10所示為同步MOSFET在有源鉗位吸收器不存在條件下的漏 極電壓。電壓偏移可能非常嚴重,達穩(wěn)態(tài)電壓的1.5倍,并且 MOSFET有可能進入雪崩條件。

圖10. 不存在有源鉗位吸收器

圖11所示為有源鉗位吸收器的有效性。前沿尖峰被完全消除, MOSFET漏極上無振鈴。

圖11. 存在有源鉗位吸收器

圖12. 0 A負載條件下的吸收器有效性

綠線:SR漏極,10 V/div

藍線:鉗位FET柵極-源極電壓,5 V/div

黃線:負載電流,10 A/div

圖13. 20 A負載條件下的吸收器有效性

綠線:SR漏極,10 V/div

藍線:鉗位FET柵極-源極電壓,5 V/div

黃線:負載電流,10 A/div

半橋拓撲結構的實驗結果

對半橋拓撲結構進行了額外的實驗驗證,額定輸入為48 V,額 定輸出為9 V、200 W,開關頻率為180 kHz。

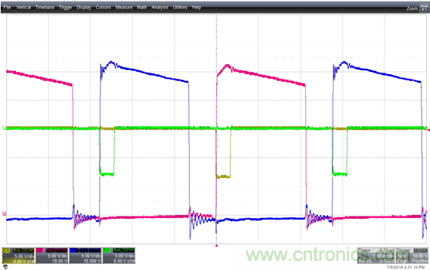

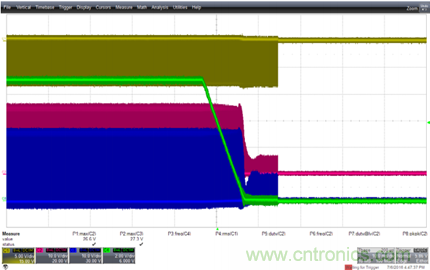

圖14. 有源鉗位吸收器禁用

紅線:SR1漏極,5 V/div

藍線:SR2漏極;5 V/div

綠線:吸收器PWM,5 V/div

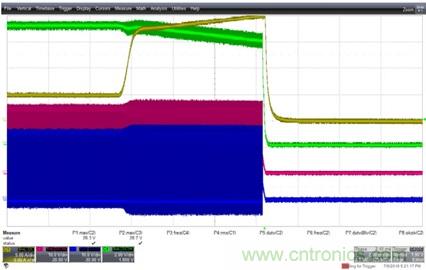

圖15. 有源鉗位吸收器使能

紅線:SR1漏極,5 V/div

藍線:SR2漏極;5 V/div

綠線:吸收器PWM,5 V/div

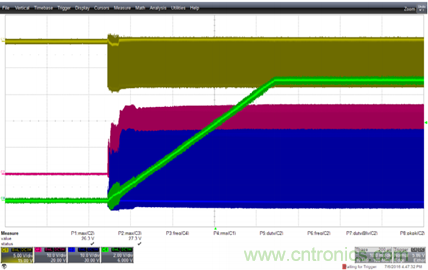

圖16. 有源鉗位吸收器條件下軟啟動期間的SR漏極波形

黃線:吸收器FET柵極-源極電壓,5 V/div

紅線:SR1漏極,10 V/div

藍線:SR2漏極,10 V/div

綠線:輸出電壓,2 V/div

圖17. 有源鉗位吸收器條件下軟啟動期間的SR漏極波形

黃線:吸收器FET柵極-源極電壓,5 V/div

紅線:SR1漏極,10 V/div

藍線:SR2漏極,10 V/div

綠線:輸出電壓,2 V/div

圖18. 短路測試過程中的SR漏極電壓

黃線:負載電流,5 A/div

紅線:SR1漏極,10 V/div

藍線:SR2漏極,10 V/div

綠線:輸出電壓,2 V/div

布局考慮

圖8所示為上述半橋拓撲結構的布局。關鍵點是通過縮短環(huán)路 或將其限制在較窄區(qū)域,減小鉗位環(huán)路的寄生電感。否則會降 低鉗位的有效性,并在鉗位周期內導致高頻振鈴。

圖19. 有源鉗位吸收器布局

結論

本文展示了有源鉗位吸收器電路在隔離式DC-DC轉換器高 輸出電流應用中的數(shù)字實現(xiàn)方式。提出的有源-鉗位方案 具有多種優(yōu)勢,比如更低的鉗位電壓,可以降低MOSFET 額定擊穿電壓, 從而提高效率。同時還消除了振鈴, 結 果可以減少電磁干擾(EMI)。這是一種低成本的簡單電路, 驅動方案也很簡單。另外, 與需要額外電感的其他有源 吸收器相比,還可以節(jié)省PCB板空間。整體而言,電源的 可靠性得到了大幅提升。此外, 消除了前沿尖峰, 結果 降低了對原邊開關的壓力。另外, 更高的效率可以降低 發(fā)熱量, 這對散熱困難的受限區(qū)域中的模塊非常有用。

ADP1055數(shù)字控制器提供了實現(xiàn)上述任務的必要工具,無需編寫 復雜的程序或代碼。ADP1055還支持多種其他功能,比如黑盒、 軟停、命令掩碼、非線性增益等。

“電子人”不可錯過的電子行業(yè)開年盛會, 2019 NEPCON上海展預登記正式開啟!

詳解射頻電路中的電感匹配

淺談電容式和熱式MEMS加速度傳感器的部分差異

超聲波風速傳感器在生活環(huán)境中的各種應用