【導(dǎo)讀】可測(cè)試性設(shè)計(jì) (DFT) 在市場(chǎng)上所有的電子設(shè)計(jì)自動(dòng)化 (EDA) 工具中是最不被重視的����,縱然在設(shè)計(jì)階段提高芯片的可測(cè)試性將會(huì)大幅縮減高昂的測(cè)試成本�����,也是如此����。最近的分析數(shù)據(jù)表明��,在制造完成后測(cè)試芯片是否存在制造缺陷的成本已增至占制造成本的 40%��,這已達(dá)到警戒水平����。

DFT 可以降低通過(guò)問(wèn)題器件的風(fēng)險(xiǎn)�,如果最終在實(shí)際應(yīng)用中才發(fā)現(xiàn)器件有缺陷,所產(chǎn)生的成本將遠(yuǎn)遠(yuǎn)高于在制造階段發(fā)現(xiàn)的成本���。它還能避免剔除無(wú)缺陷器件���,從而提高良率。插入 DFT 亦能縮短與測(cè)試開(kāi)發(fā)相關(guān)的時(shí)間����,并減少測(cè)試裝配好的芯片所需的時(shí)間。

DFT 是電子行業(yè)的警鐘�����,它采用自動(dòng)測(cè)試模式生成器 (ATPG) 和存儲(chǔ)內(nèi)置自測(cè)試 (MBIST)�,是在芯片上插入測(cè)試結(jié)構(gòu)(例如掃描鏈���、MBIST 結(jié)構(gòu)或壓縮/解壓邏輯)。掃描鏈通過(guò)串行移位寄存器增加了可控性和可觀察性�����。借助掃描鏈�,測(cè)試電路的工作得到簡(jiǎn)化和縮減。使用 ATPG 工具自動(dòng)生成測(cè)試模式能夠減少耗時(shí)繁瑣的測(cè)試向量創(chuàng)建任務(wù)��。

當(dāng)設(shè)計(jì)經(jīng)過(guò)功能驗(yàn)證后��,片上測(cè)試架構(gòu)(或掃描鏈)會(huì)在門(mén)級(jí)的基礎(chǔ)上被插入�,執(zhí)行此操作時(shí)必須小心謹(jǐn)慎,因?yàn)檫@可能會(huì)影響芯片的功能正確性��。設(shè)計(jì)更改需要進(jìn)行門(mén)級(jí)驗(yàn)證��,以確保設(shè)計(jì)完整性未受影響�。測(cè)試將由測(cè)試模式的長(zhǎng)序列執(zhí)行�����,這是一項(xiàng)計(jì)算密集型任務(wù)���,比寄存器傳輸級(jí) (RTL) 驗(yàn)證繁瑣得多�����。

值得一提的是����,從設(shè)計(jì)角度而言,創(chuàng)建并插入 DFT 結(jié)構(gòu)是一項(xiàng)十分簡(jiǎn)單的工作���。不過(guò)���,從密度和規(guī)模的層面來(lái)看����,設(shè)計(jì)規(guī)模會(huì)增加��,同時(shí)測(cè)試設(shè)計(jì)所需的測(cè)試模式數(shù)量也會(huì)使設(shè)計(jì)規(guī)模大大增加�。

DFT 驗(yàn)證

當(dāng)設(shè)計(jì)尺寸達(dá)到數(shù)億門(mén)時(shí)����,基于軟件仿真器的驗(yàn)證對(duì)于門(mén)級(jí)檢查而言速度過(guò)于緩慢�。DFT 方法只會(huì)讓事情變得更糟�。如果這些負(fù)擔(dān)還能夠應(yīng)付��,那么優(yōu)先使用軟件仿真陣列來(lái)推進(jìn)流片有助于設(shè)計(jì)工程師的工作�����,但會(huì)為測(cè)試工程師帶來(lái)阻礙�。芯片通常只進(jìn)行極少的 DFT 驗(yàn)證就進(jìn)行流片��,而在流片后才執(zhí)行徹底的 DFT 測(cè)試�����,這時(shí)要修復(fù)設(shè)計(jì)缺陷為時(shí)已晚。

DFT 驗(yàn)證具有多種形式��,包括需要驗(yàn)證的自定義初始化模式����。它可以是由自動(dòng)測(cè)試模式生成器工具插入的片上時(shí)鐘控制器,這需要在模式執(zhí)行期間進(jìn)行動(dòng)態(tài)驗(yàn)證��;也可以是為 MBIST 添加的邏輯�����,這通常需要對(duì)測(cè)試模式的相關(guān)邏輯進(jìn)行功能驗(yàn)證���。SoC 可能包括一個(gè)自定義初始化模式��,此模式能夠配置測(cè)試并完成從功能模式到測(cè)試模式的轉(zhuǎn)換�。其他測(cè)試模式可能會(huì)采用低功耗技術(shù)�,測(cè)試期間,芯片的一部分將進(jìn)入低功耗模式��,這就需要在適當(dāng)情況下的有效測(cè)試結(jié)構(gòu)���。

使用 DFT App 進(jìn)行硬件加速仿真

硬件加速能夠縮短執(zhí)行徹底 DFT 驗(yàn)證所需的仿真周期��。同時(shí)還能驗(yàn)證各種規(guī)模和復(fù)雜性的芯片的功能�����。

30 年來(lái)����,人們一直使用硬件加速仿真部署可重復(fù)編程的硬件來(lái)增加驗(yàn)證周期�,而新的部署模式使這項(xiàng)技術(shù)成為更可行的驗(yàn)證工具,同時(shí)也為“App”的方法奠定基礎(chǔ)�。對(duì)于仍受困于基于軟件仿真器進(jìn)行驗(yàn)證的芯片設(shè)計(jì)團(tuán)隊(duì)而言,近期推出的一些硬件加速仿真應(yīng)用程序無(wú)疑是個(gè)好消息���。DFT App 能夠加速需要進(jìn)行全面門(mén)級(jí)仿真的芯片設(shè)計(jì)進(jìn)程����。借助自動(dòng)生成的模式��,設(shè)計(jì)團(tuán)隊(duì)能夠縮短整個(gè)模式開(kāi)發(fā)周期�����。

這類(lèi)硬件加速仿真的可擴(kuò)展硬件和編譯器能夠?qū)η度肓藪呙韬推渌麥y(cè)試結(jié)構(gòu)的大型門(mén)級(jí)設(shè)計(jì)進(jìn)行測(cè)試模式驗(yàn)證。它具有出色性能�,能夠運(yùn)行更多仿真周期,加快 DFT 分析��。DFT App 支持行業(yè)標(biāo)準(zhǔn) STIL 格式文件�����,可以與其他工具協(xié)同工作���,STIL 文件可用于生產(chǎn)測(cè)試程序以便在制造過(guò)程中發(fā)現(xiàn)受損芯片��。

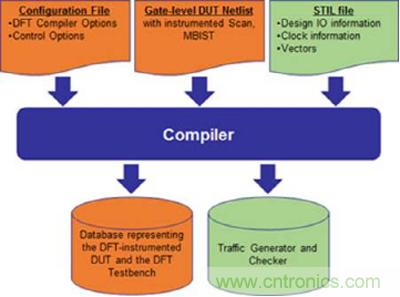

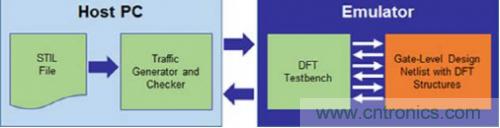

用于硬件加速仿真的 DFT App 改變了硬件加速器在開(kāi)發(fā)階段的編譯流程和運(yùn)行時(shí)間����。這將為編譯流程和運(yùn)行時(shí)間帶來(lái)重大變化�����。具有掃描和 MBIST 結(jié)構(gòu)的門(mén)級(jí)設(shè)計(jì)被載入硬件加速仿真的編譯器�。編譯器創(chuàng)建了用于讀取Stil文件中測(cè)試向量的測(cè)試結(jié)構(gòu),然后將這些向量應(yīng)用到可綜合的待測(cè)器件 (DUT) 以及進(jìn)行輸出比較�。編譯器將用戶(hù)網(wǎng)表重新編譯并合成到一個(gè)能夠兼容硬件加速仿真的結(jié)構(gòu)化描述中。編譯器創(chuàng)建了用于讀取Stil文件中測(cè)試向量的測(cè)試結(jié)構(gòu)��,然后將這些測(cè)試向量用到可綜合的待測(cè)設(shè)計(jì)上,再將網(wǎng)表重新編譯并合成到一個(gè)能夠兼容硬件加速仿真的結(jié)構(gòu)化描述中���。測(cè)試控制架構(gòu)還包括比較輸出的機(jī)制��。參見(jiàn)圖 1。

圖 1:經(jīng) DFT App 修改后的編譯流程�。

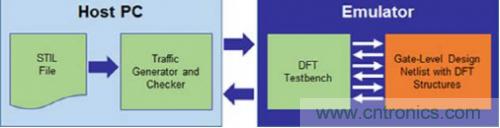

調(diào)用時(shí),設(shè)計(jì)和測(cè)試平臺(tái)被映射到硬件加速器中�。在運(yùn)行期間,硬件加速仿真從 STIL 文件中提取測(cè)試向量�����,然后將其應(yīng)用于 DUT 并比較輸出����,這一切都是以硬件加速仿真的速度完成。參見(jiàn)圖 2�。

圖 2:顯示主機(jī) PC 和硬件加速器操作分解的運(yùn)行時(shí)間方框圖。

DFT App 可執(zhí)行完整的 DFT 驗(yàn)證模式設(shè)置���,從而縮短模式開(kāi)發(fā)周期�����。通過(guò)結(jié)合可處理多達(dá)數(shù)十億個(gè)門(mén)的可擴(kuò)展硬件加速仿真平臺(tái)以及支持 DFT 方法的編譯器�,能夠?qū)σ亚度霋呙韬推渌麥y(cè)試結(jié)構(gòu)的大型門(mén)級(jí)設(shè)計(jì)進(jìn)行測(cè)試模式驗(yàn)證。

完成芯片制造后�����,相同的 STIL 文件亦能夠在測(cè)試車(chē)間使用�����。將測(cè)試向量載入 ATE���,對(duì)芯片執(zhí)行測(cè)試���,并將響應(yīng)結(jié)果與 STIL 文件中的預(yù)期數(shù)值相比較。

可測(cè)試性設(shè)計(jì)

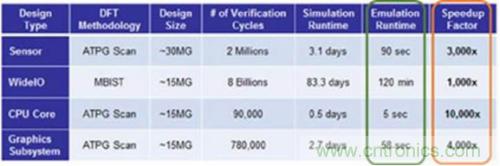

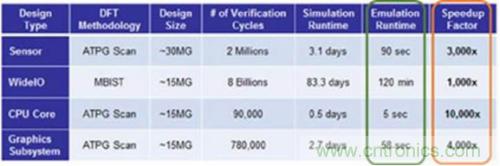

硬件加速仿真的執(zhí)行速度比軟件仿真高出幾個(gè)數(shù)量級(jí)�����,而不是小幅增加�。在硬件加速仿真中運(yùn)行 DFT 模式時(shí),某些衡量標(biāo)準(zhǔn)提高了四到五個(gè)數(shù)量級(jí)����。參見(jiàn)表 1�����。

表 1:體現(xiàn)了性能改進(jìn)的 DFT App 基準(zhǔn)數(shù)據(jù)對(duì)比

對(duì)于軟件仿真器通常需要三個(gè)月才能完成的測(cè)試��,硬件加速仿真只需兩小時(shí)就能完成�,從而可在芯片流片前對(duì)測(cè)試向量和 DFT 邏輯進(jìn)行完整驗(yàn)證��。將 DFT App 應(yīng)用于硬件加速仿真中����,拓展了使用方式����、提高性能,并幫助驗(yàn)證工程師規(guī)避風(fēng)險(xiǎn)����。借助硬件加速器的強(qiáng)大功能,DFT 工程師現(xiàn)在已能使用“App”來(lái)確保芯片適合進(jìn)入制造流程�����。