【導(dǎo)讀】前面小編為大家講到《時序約束的一些經(jīng)驗(yàn)》,這一節(jié)中將談?wù)撎砑蛹s束后進(jìn)行綜合,如果出現(xiàn)時序違規(guī),會是哪類情況以及該如何去解決。想學(xué)習(xí)這方面知識的童鞋可千萬別錯過,不然后悔別找我??!

通常來講,一項(xiàng)芯片或者FPGA項(xiàng)目工程走到綜合這一步說是到了尾聲,其實(shí)恰恰才是剛剛開始,后面還有很多很多的流程和路要走,所以解決時序違規(guī)問題十分重要,如果這個問題解決不好,后面的流程就沒法往下走,整個項(xiàng)目可能停滯不前,甚至打回到最開始重新進(jìn)行coding,如果在不幸運(yùn)的話有可能整個項(xiàng)目就會fail,所以時序分析及解決違規(guī)問題則是必須攻克的一個難題。

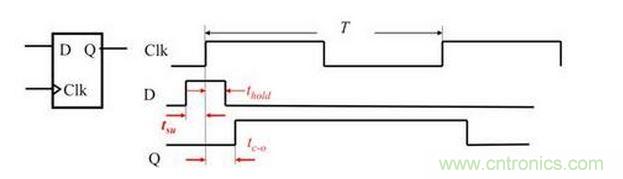

其實(shí)所有的時序問題都可以歸結(jié)為常見的兩類問題:建立時間(setup time)和保持時間(hold time)的問題,關(guān)于他們的定義大家可以百度一下。

1)一般呢,建立時間不滿足往往是由于組合邏輯團(tuán)太大的原因造成的;保持時間不滿足往往是由于組合邏輯團(tuán)太小的原因造成的;建立時間和保持時間都不滿足的情況往往是出現(xiàn)在異步時鐘域中。

2)解決建立時間不滿足的方法有如下:加強(qiáng)約束,重新進(jìn)行綜合,對違規(guī)的路勁進(jìn)行進(jìn)一步的優(yōu)化,但是一般效果可能不是很明顯;降低時鐘的頻率或者提高電路的電壓,但是這個一般是在項(xiàng)目最初的時候決定的,這個時候很難再改變;拆分組合邏輯團(tuán)插入寄存器,增加流水線,這個是常用的方法;盡量減小傳輸?shù)难訒r;換用先進(jìn)的工藝,但是這個一般也不太現(xiàn)實(shí)。所以流水線是常用的方法。

3)解決保持時間不滿足的方法有如下:增加邏輯團(tuán)的延時,一般就是在后端的時候插入buffer;減小時鐘的延時。相比建立時間,保持時間的問題一般比較好解決。

4)異步時鐘域的問題:這個一般要單獨(dú)依靠異步時鐘域(CDC)處理的方法來解決。

所以整體而言,處理時鐘問題其實(shí)就是在處理建立時間,保持時間,異步時鐘等相關(guān)的問題,把這些解決好,后面才能順利的進(jìn)行。

在后續(xù)中,會更為詳細(xì)的,圖文并茂的介紹如何處理建立時間和保持時間的方法,如何處理CDC的問題。希望大家耐心等待!