【導(dǎo)讀】本文跟大家分享的是來自西門子公司的一個(gè)和探頭,接地相關(guān)的真實(shí)調(diào)試案例,有些電路本來沒有問題,連接上探頭就有問題了;有些電路本來有問題,接上探頭又沒有問題了。這兩種情況的根源在哪呢?怎么發(fā)現(xiàn)他?就跟小編來看看示波器作為工程師眼睛是如何幫助大家解決問題的?

又是一個(gè)和探頭,接地相關(guān)的真實(shí)調(diào)試案例!

有些電路本來沒有問題,連接上探頭就有問題了;有些電路本來有問題,接上探頭又沒有問題了。兩種情況下的根源可能大不一樣,但一定是有一個(gè)沒有被挖出來的根源。

來自西門子公司的李工和R&S的李工一起,追根溯源,搞明白了原來問題出在晶振的"來料不良"上。這令筆者想起有位老采購說的:最容易出問題的物料就三樣:電源,晶振和接插件。在發(fā)現(xiàn)問題的過程中,我們可以看到示波器作為"工程師的眼睛"的價(jià)值。

2014年7月份,我們啟動(dòng)了電能質(zhì)量高端設(shè)備開發(fā)項(xiàng)目。這個(gè)項(xiàng)目的技術(shù)需求是采樣點(diǎn)多,數(shù)據(jù)率高,算法復(fù)雜,數(shù)據(jù)存儲(chǔ)量大,網(wǎng)絡(luò)接口多,高級(jí)應(yīng)用多等。面臨這樣的情況,我們通過大量分析和評(píng)估,決定新構(gòu)建硬件平臺(tái)來滿足產(chǎn)品需求。通過對(duì)多家處理器進(jìn)行分析? 比對(duì),最終一個(gè)全新的硬件架構(gòu)出爐了:以雙核CPU配上FPGA,Switch,DOM盤等來實(shí)現(xiàn)數(shù)據(jù)獲取,傳輸,計(jì)算,存儲(chǔ),通信等功能。經(jīng)過一番努力,很快我們的板卡打樣回板,并完成了SMT,正式進(jìn)入軟硬件調(diào)試階段。在完成小系統(tǒng)(CPU,DDR,F(xiàn)lash等)主要器件測(cè)試后,我們進(jìn)入小系統(tǒng)外圍器件的開發(fā)環(huán)節(jié),在做SATA-DOM盤測(cè)試時(shí),發(fā)現(xiàn)了DOM盤無法連接的問題。在軟件工程師的配合測(cè)試下,很快定位出是差分晶振輸出給CPU的差分LVDS參考時(shí)鐘未能穩(wěn)定鎖定,導(dǎo)致控制器無法正常工作。在公司內(nèi)部尋找測(cè)試高速信號(hào)的示波器,發(fā)現(xiàn)基本都是帶寬很低的示波器,且不配有有源差分探頭,根本無法看到波形,從而無法判斷是原理設(shè)計(jì)問題,還是PCB,或器件焊接及其它問題,項(xiàng)目就此卡住了。接下來就是一頓滿地找能用的示波器過程了,那個(gè)汗?。?/div>

真是趕巧,我們公司早準(zhǔn)備配置高端示波器了,由于采購流程很長(zhǎng),一直處于在Tek,R&S,Agilent三家聯(lián)系和產(chǎn)品評(píng)估中。通過我們的采購很快聯(lián)系上這三家公司的銷售,R&S是在聯(lián)系之后,以最快的速度,率先給我們發(fā)來測(cè)試示波器樣機(jī)的廠家,正是雪中送碳,久旱逢甘霖啊!拿到示波器測(cè)試樣機(jī)的當(dāng)天,筆者就快速拆封上電,準(zhǔn)備信號(hào)測(cè)試了。由于之前一直用另外兩家的示波器,初始使用R&S的示波器,其軟件界面及操作按鈕均不是很熟悉,操作起來相對(duì)生澀。經(jīng)過簡(jiǎn)單摸索后,基本能做簡(jiǎn)單測(cè)試了,但是要進(jìn)行高速信號(hào)測(cè)量還不能快速搞定,只能求助技術(shù)支持了。通過采購順利聯(lián)系上銷售工程師-楊毓,在其幫助下,又快速聯(lián)系上了技術(shù)支持工程師-李星。在李工的遠(yuǎn)程協(xié)助下,很快可以進(jìn)行高速信號(hào)測(cè)量,并抓到了時(shí)鐘波形。李工擔(dān)心筆者這邊搞不好,又在第二天上午趕到我們公司,進(jìn)行現(xiàn)場(chǎng)培訓(xùn)指導(dǎo)?;谧サ降臅r(shí)鐘波形,我們展開全面分析,李工深厚的技術(shù)知識(shí),對(duì)筆者這個(gè)詭異問題的分析提供了重要思路。

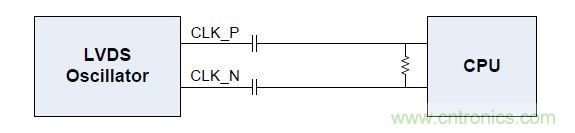

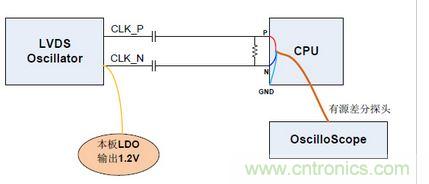

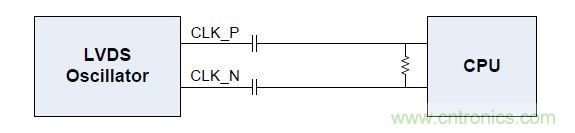

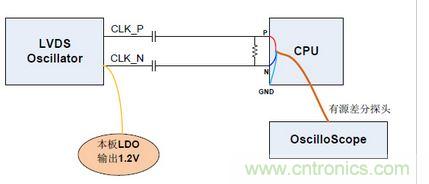

先是原理分析,初步結(jié)論是:硬件原理設(shè)計(jì)上不存在太多的問題。這是一個(gè)LVDS時(shí)鐘晶振發(fā)出差分LVDS 時(shí)鐘后,通過交流耦合連到CPU側(cè)(圖)。

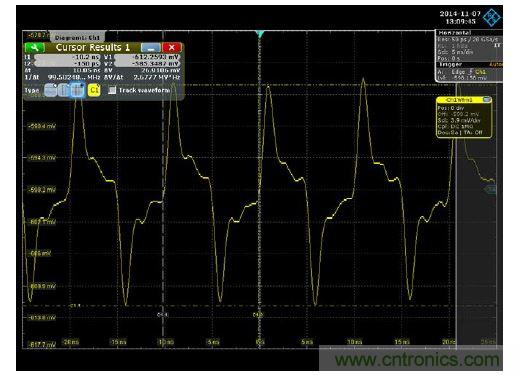

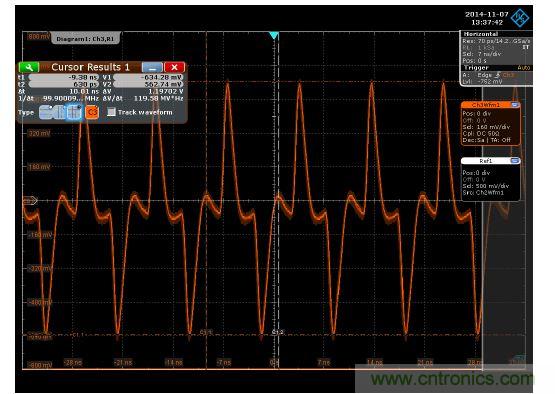

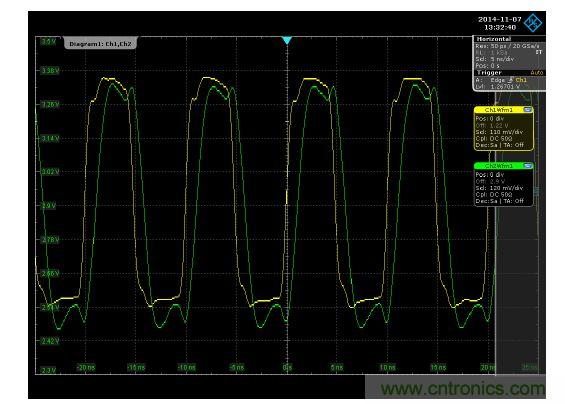

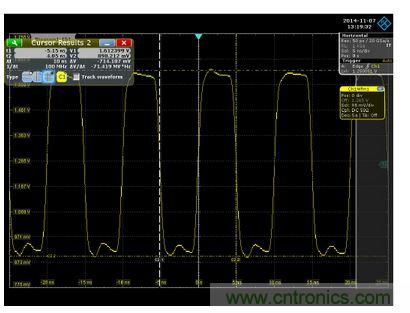

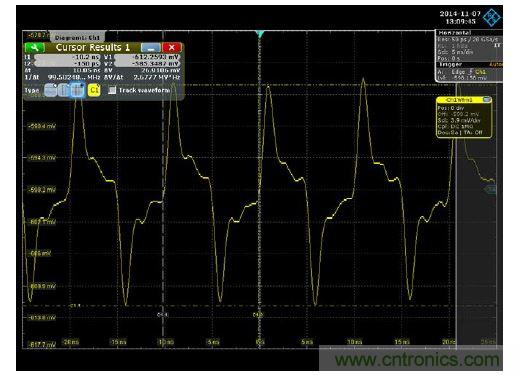

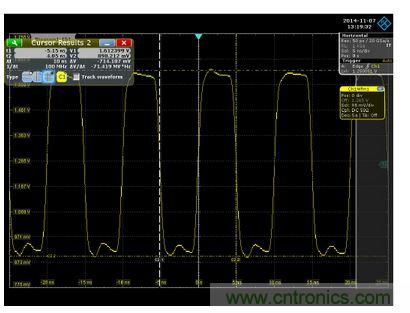

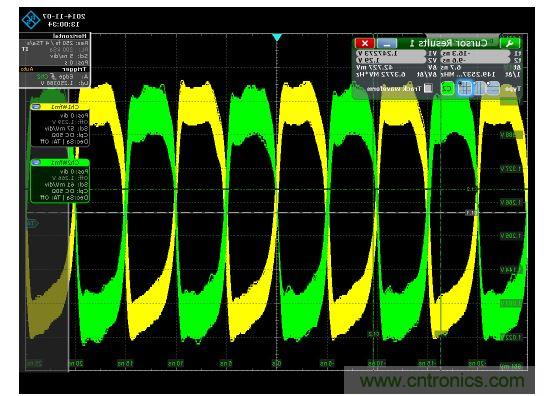

原理上找不到問題,只能集中精力測(cè)量波形并進(jìn)行詳細(xì)分析了。通過R&S示波器,用有源差分探頭(圖1)和有源單端探頭在CPU側(cè)來捕獲時(shí)鐘輸出波形(圖2)。

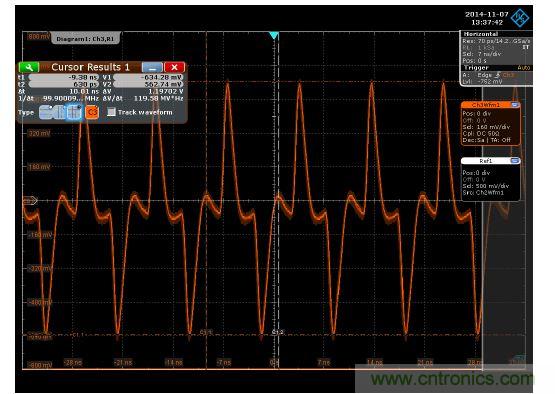

圖1差分探頭測(cè)得圖

[page]

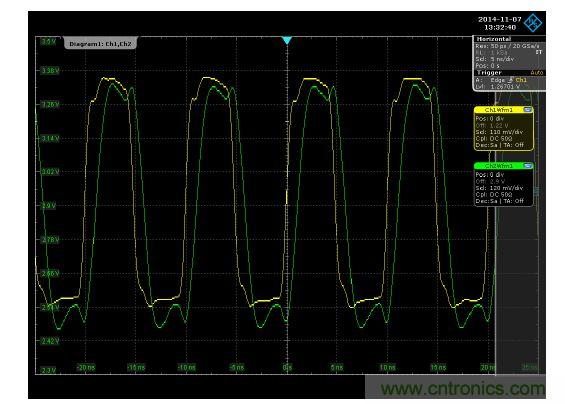

圖2單端探頭測(cè)得圖

從圖可知:時(shí)鐘質(zhì)量在CPU端差,信號(hào)差分?jǐn)[幅不夠,而且共模電壓超出范圍,且波形畸變嚴(yán)重。CPU側(cè)的PLL針對(duì)這個(gè)輸入時(shí)鐘信號(hào)無法鎖定,也是理所但然的。難道是PCB設(shè)計(jì)有問題?

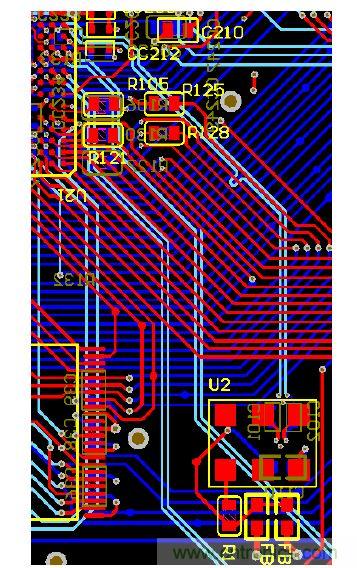

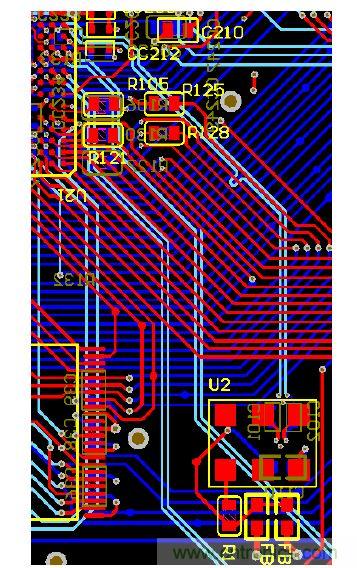

PCB走線的截圖如下:

圖中:U2為差分晶振,晶振背面的C101和C102為交流耦合電容。PCB的走線為:線寬8mil,線間距16mil,差分等長(zhǎng)控制在5mil,總線長(zhǎng)1550mil(小于器件資料的2000mil)。

再仔細(xì)分析PCB設(shè)計(jì),滿足器件資料的布局布線要求,且也符合多年高速設(shè)計(jì)經(jīng)驗(yàn)。理論上應(yīng)該不存在問題,怎么會(huì)有這么奇怪的波形呢?難道是CPU負(fù)載側(cè)有問題?聯(lián)系CPU的技術(shù)支持,通過對(duì)原理圖和PCB分析,很快得到一些可能存在問題的信息:末端跨接電阻是否焊接,芯片接地是否正確等等。通過實(shí)驗(yàn),依次排除這些因素。

那么此時(shí),只能進(jìn)行全面信號(hào)測(cè)量詳細(xì)分析了。首先是晶振外圍電路測(cè)量。應(yīng)用R&S的示波器,選擇交流耦合測(cè)量方式,發(fā)現(xiàn)晶振的供電電源紋波很大,3.3V直流電的紋波達(dá)到100mv左右,由于這個(gè)供電來自DC/DC電源,存在這么大的紋波有可能導(dǎo)致晶振輸出異常。飛線取LDO輸出的3.3V(確認(rèn)紋波小于10mv),再次測(cè)試發(fā)現(xiàn)PLL仍然不能鎖定,CPU側(cè)測(cè)試波形依然不符合LVDS信號(hào)標(biāo)準(zhǔn)。但是在測(cè)量過程中偶然發(fā)現(xiàn)一個(gè)異常,就是用R&S單端無源探頭來測(cè)量晶振輸出側(cè)的信號(hào)電壓時(shí),發(fā)現(xiàn)PLL竟然鎖上了。此時(shí)是將單端探頭的接地線接在LVDS信號(hào)的負(fù)端,探針頂住信號(hào)正端。這是個(gè)什么情況,百思不得其解啊……完全顛覆了我們的認(rèn)識(shí)了?,F(xiàn)在開始懷疑,該差分晶振是否存在質(zhì)量問題。

[page]

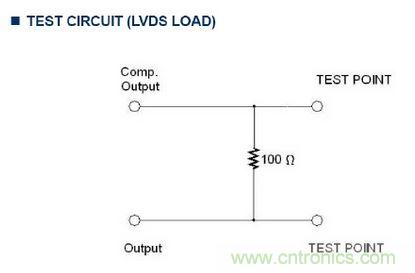

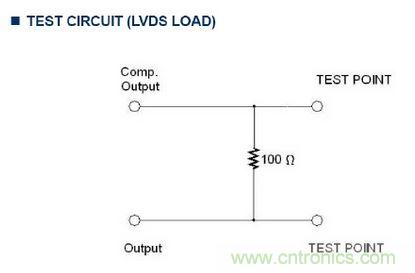

那么接下來針對(duì)晶振,根據(jù)器件提供的廠家資料中描述的測(cè)試方式進(jìn)行裸片供電測(cè)量。其圖紙:(圖3)

圖3 推薦測(cè)試電路

將晶振直接飛線供上3.3V的電,斷開現(xiàn)有負(fù)載,在差分PN信號(hào)間跨接100歐電阻,再進(jìn)行信號(hào)測(cè)量,發(fā)現(xiàn)晶振輸出確實(shí)有問題,其差分信號(hào)和單端信號(hào)輸出擺幅小,信號(hào)畸變嚴(yán)重(與圖1和圖2類似)。由此,基本可以得出結(jié)論:那就是晶振通過非正規(guī)途徑購買的,其質(zhì)量之差,唉,無語?。?根據(jù)上述測(cè)試情況,這里總結(jié)了有兩個(gè)問題,分別制定驗(yàn)證解決方案:

o 通過正規(guī)渠道,再購買差分晶振,準(zhǔn)備測(cè)試;

o 分析為什么在R&S示波器無源探頭地線接到差分信號(hào)負(fù)端的情況,能使信號(hào)質(zhì)量改善;

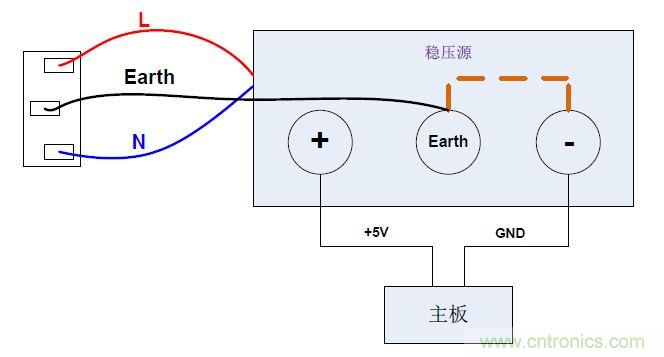

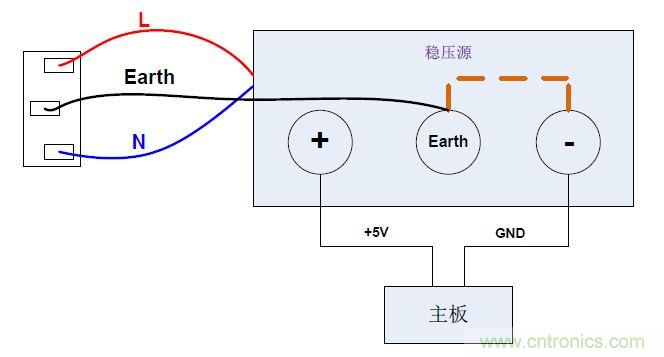

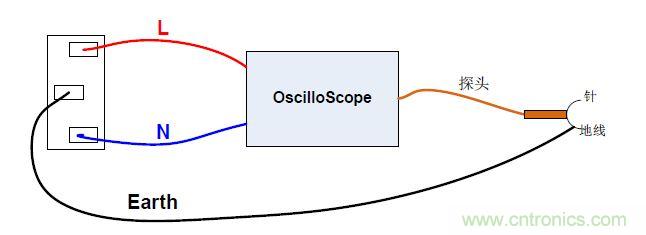

針對(duì)方案二,模擬探頭標(biāo)明的電阻,電容分布參數(shù),又進(jìn)行了一些試驗(yàn):例如負(fù)端飛線,通過串聯(lián)電阻,電容等方式接地,均無法匹配探頭底線接觸的現(xiàn)象。后來仔細(xì)分析發(fā)現(xiàn),筆者的單板供電直流穩(wěn)壓電源的輸出電壓的地線與市電電力線未共地(圖4),即圖中虛線未連接。此時(shí),用萬用表測(cè)試示波器探頭的地線與直流源(-端)輸出的GND 之間,發(fā)現(xiàn)有個(gè)很小的電壓壓差。

圖4 測(cè)試組網(wǎng)圖

[page]

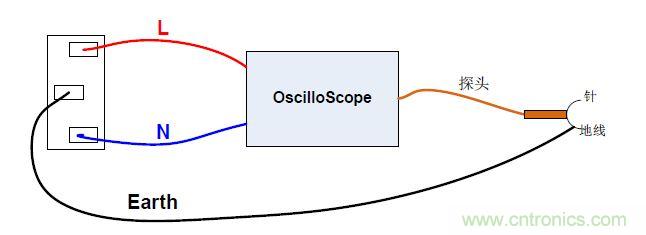

當(dāng)完成Earth共地后(接上虛線),采用下圖5組網(wǎng)測(cè)試,此時(shí)PLL仍無法鎖存,再用示波器探頭的地線連接差分信號(hào)負(fù)極時(shí),PLL也無法鎖定了。

圖5 工地測(cè)試組網(wǎng)圖

由此可見,這個(gè)問題與示波器及探頭本身沒有關(guān)系。通過分析發(fā)現(xiàn):由于探頭地接的是電力線準(zhǔn)大地,與穩(wěn)壓電源輸出地之間是浮空關(guān)系,存在一些電壓差。此時(shí)得出結(jié)論,在當(dāng)前不良的晶振負(fù)端接入某個(gè)幅度的直流電壓時(shí),相當(dāng)于提高了差分晶振輸入的共模電壓,一定程度上改善LVDS信號(hào)的質(zhì)量。因此,做了另外一個(gè)實(shí)驗(yàn),通過將差分晶振負(fù)端飛線到1.2V電壓上(圖6),人為提供1.2V共模電壓,這時(shí)發(fā)現(xiàn)PLL鎖定成功,DOM盤正常工作了。

圖6 差分信號(hào)負(fù)極飛線測(cè)試圖

此時(shí)用有源差分和有源單端探頭測(cè)得波形:

圖7 有源差分探頭測(cè)得圖

[page]

圖8 有源單端測(cè)得圖

從上兩張圖可得:盡管PLL鎖定了,但是還能看出P,N信號(hào)不是180度交叉的,共模電壓也不對(duì),但是此時(shí)的差分信號(hào)擺幅夠大見圖7,能夠使LVDS的PLL工作。

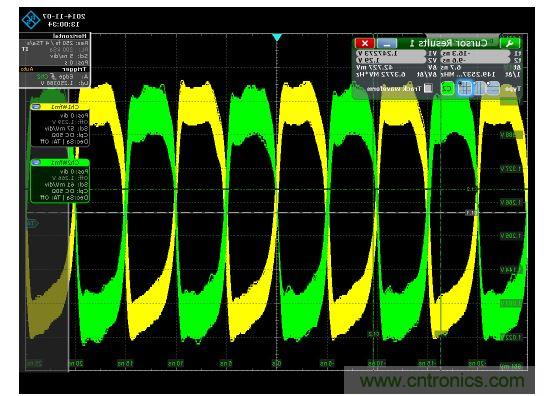

針對(duì)第一種方案,我們采購到了臺(tái)灣某家公司的差分晶振,焊接完后,SATA-DOM直接就能穩(wěn)定工作了,進(jìn)一步驗(yàn)證了初始使用的差分晶振是存在質(zhì)量問題的。當(dāng)然,針對(duì)新的差分晶振,我們也進(jìn)行 了詳細(xì)的波形測(cè)試圖9和圖10,發(fā)現(xiàn)指標(biāo)與器件資料一致,且符合LVDS 信號(hào)標(biāo)準(zhǔn)。且針對(duì)DOM盤進(jìn)行讀寫文件壓力測(cè)試,到目前為止工作正常,這個(gè)問題也得到了圓滿的解決。

圖9 有源差分探頭測(cè)得圖

圖10 有源單端測(cè)得圖

在整個(gè)問題定位解決過程中,R&S示波器確實(shí)起到了"工程師眼睛"的作用,對(duì)高速被測(cè)信號(hào)的準(zhǔn)確測(cè)量,并拿到想要的波形,給我們分析問題提供了有力的證據(jù),方便迅捷的窗口界面觸摸操作,大大提升了測(cè)量的速度。