【導(dǎo)讀】對(duì)FPGA芯片而言,在給芯片加電工作前,芯片內(nèi)部各個(gè)節(jié)點(diǎn)電位的變化情況均不確定、不可控,而這種不確定且不可控的情況會(huì)使芯片在上電后的工作狀態(tài)出現(xiàn)錯(cuò)誤。那么如何設(shè)計(jì)出高可靠性的FPGA呢?

對(duì)FPGA設(shè)計(jì)中常用的復(fù)位設(shè)計(jì)方法進(jìn)行了分類、分析和比較。針對(duì)FPGA在復(fù)位過程中存在不可靠復(fù)位的現(xiàn)象,提出了提高復(fù)位設(shè)計(jì)可靠性的4種方法,包括清除復(fù)位信號(hào)上的毛刺、異步復(fù)位同步釋放、采用專用全局異步復(fù)位/置位資源和采用內(nèi)部復(fù)位。上述方法可有效提高FPGA復(fù)位的可靠性。

對(duì)FPGA芯片而言,在給芯片加電工作前,芯片內(nèi)部各個(gè)節(jié)點(diǎn)電位的變化情況均不確定、不可控,而這種不確定且不可控的情況會(huì)使芯片在上電后的工作狀態(tài)出現(xiàn)錯(cuò)誤。因此,在FPGA的設(shè)計(jì)中,為保證系統(tǒng)能可靠進(jìn)進(jìn)入工作狀態(tài),以及避免對(duì)FPGA輸出關(guān)聯(lián)的系統(tǒng)產(chǎn)生不良影響,F(xiàn)PGA上電后要進(jìn)行復(fù)位,且為了消除電源開關(guān)過程中引起的抖動(dòng)影響,復(fù)位信號(hào)需在電源穩(wěn)定后經(jīng)過一定的延時(shí)才能撤銷,F(xiàn)PGA的復(fù)位信號(hào)需保證正確、穩(wěn)定、可靠。

在FPGA的設(shè)計(jì)中,多數(shù)情況下復(fù)位電路的功能雖能夠正常完成,但電路并未得到精確合理的設(shè)計(jì),仍存在可靠性設(shè)計(jì)缺陷。為確保系統(tǒng)復(fù)位的可靠性,有必要對(duì)FPGA復(fù)位的可靠性設(shè)計(jì)方法進(jìn)行研究。

1復(fù)位設(shè)計(jì)方法分類

復(fù)位的目的是在仿真時(shí)將設(shè)計(jì)強(qiáng)制定位在一個(gè)可知狀態(tài),合理選擇復(fù)位方式是電路設(shè)計(jì)的關(guān)鍵。根據(jù)與系統(tǒng)時(shí)鐘域的關(guān)系,復(fù)位電路可分為同步復(fù)位和異步復(fù)位。同步復(fù)位是指復(fù)位信號(hào)只在時(shí)鐘沿到來時(shí),才有效。否則,無法完成對(duì)系統(tǒng)的復(fù)位工作。異步復(fù)位是指無論時(shí)鐘沿是否到來,只要復(fù)位信號(hào)有效,使對(duì)系統(tǒng)進(jìn)行復(fù)位。

根據(jù)是否存在外部復(fù)位端口,復(fù)位電路又可分為外部復(fù)位和內(nèi)部復(fù)位。外部復(fù)位是指復(fù)位信號(hào)主要來自外部引腳的輸入,如復(fù)位按鈕、電源模塊輸出等。內(nèi)部復(fù)位信號(hào)則是主要由FPGA內(nèi)部電路產(chǎn)生。

2復(fù)位設(shè)計(jì)方法的比較

2.1同步復(fù)位與異步復(fù)位

2.2.1同步復(fù)位

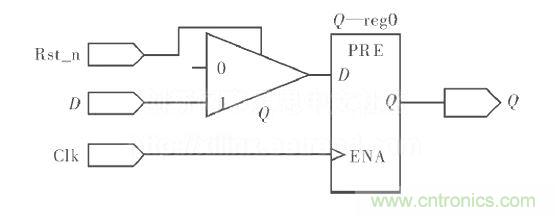

指定同步復(fù)位時(shí),always的敏感表中僅有一個(gè)時(shí)鐘沿信號(hào),只有當(dāng)時(shí)鐘沿采集到同步復(fù)位的有效電平時(shí),才會(huì)在時(shí)鐘沿到達(dá)時(shí)刻進(jìn)行復(fù)位操作。若目標(biāo)器件或可用庫中的觸發(fā)器本身包含同步復(fù)位端口,則在實(shí)現(xiàn)同步復(fù)位電路時(shí)可直接調(diào)用同步復(fù)位端。然而多數(shù)目標(biāo)器件的觸發(fā)器本身并不包含同步復(fù)位端口,需使復(fù)位信號(hào)與輸入信號(hào)組成某種組合邏輯,然后將其輸入到寄存器的輸入端。為了提高復(fù)位電路的優(yōu)先級(jí),通常在電路描述時(shí)使用帶有優(yōu)先級(jí)的if…else結(jié)構(gòu),復(fù)位電路在第一個(gè)if下描述,其他電路在else或else…if分支中描述。復(fù)位電路綜合后的RTL圖如圖1所示。

圖1同步復(fù)位電路圖

根據(jù)同步電路的特點(diǎn),其電路優(yōu)點(diǎn)有:(1)同步復(fù)位有利于基于周期機(jī)制的仿真器進(jìn)行仿真。(2)使用同步復(fù)位可設(shè)計(jì)100%的同步時(shí)序電路,有利于時(shí)序分析,其綜合結(jié)果的頻率較高。(3)同步復(fù)位僅在時(shí)鐘的有效沿生效,可有效避免因毛刺造成的亞穩(wěn)態(tài)和錯(cuò)誤。毛刺信號(hào)是由FPGA內(nèi)部結(jié)構(gòu)特征決定的,同步復(fù)位在進(jìn)行復(fù)位和釋放復(fù)位信號(hào)時(shí),僅當(dāng)時(shí)鐘沿采到復(fù)位信號(hào)電平變化時(shí)進(jìn)行相關(guān)操作,若復(fù)位信號(hào)樹的組合邏輯出現(xiàn)了某種毛刺,此時(shí)時(shí)鐘沿采到毛刺的概率較低,由此通過時(shí)鐘沿采樣,可有效過波復(fù)位電路組合邏輯產(chǎn)生的毛刺,增強(qiáng)了電路穩(wěn)定性。

同步復(fù)位的缺點(diǎn)有:(1)多數(shù)目標(biāo)器件庫的觸發(fā)器本身并不包含同步復(fù)位端口,使用同步復(fù)位會(huì)增加更多邏輯資源。(2)同步復(fù)位的最大問題在于必須保證復(fù)位信號(hào)的有效時(shí)間,需要一個(gè)脈寬延展器以確保復(fù)位信號(hào)有一定脈沖寬度,由此才能保證所有觸發(fā)器均能有效復(fù)位。由于同步復(fù)位僅當(dāng)時(shí)鐘沿采到復(fù)位信號(hào)時(shí)才會(huì)進(jìn)行復(fù)位操作,所以其信號(hào)的持續(xù)時(shí)間要大于設(shè)計(jì)的最長(zhǎng)時(shí)鐘周期,以保證所有時(shí)鐘的有效沿都能采樣到同步復(fù)位信號(hào)。事實(shí)上,僅保證同步復(fù)位信號(hào)的持續(xù)時(shí)間大于最慢的時(shí)鐘周期是不夠的,設(shè)計(jì)中還需考慮到同步復(fù)位信號(hào)樹通過所有相關(guān)組合邏輯路徑時(shí)的延時(shí),以及由于時(shí)鐘布線產(chǎn)生的偏斜。只有同步復(fù)位大于時(shí)鐘最大周期,加上同步信號(hào)穿過的組合邏輯路徑延時(shí)和時(shí)鐘偏斜延時(shí),才能確保同步復(fù)位的可靠。

[page]

2.2.2異步復(fù)位

指定異步復(fù)位時(shí),只需在always的敏感表中加人復(fù)位信號(hào)的有效沿即可,當(dāng)復(fù)位信號(hào)有效沿到達(dá)時(shí),無論時(shí)鐘沿是否有效,復(fù)位均會(huì)立即發(fā)揮其功能。

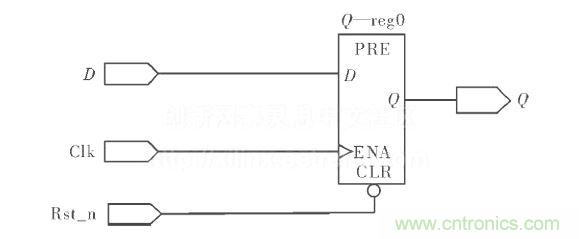

大多數(shù)目標(biāo)器件和ASIC庫的觸發(fā)器均包含異步復(fù)位端口,異步復(fù)位會(huì)直接接人觸發(fā)器的異步復(fù)位端口,綜合后的RTL圖如圖2所示。

圖2異步復(fù)位電路圖

根據(jù)異步電路的特點(diǎn),異步復(fù)位的優(yōu)點(diǎn)有:(1)由于多數(shù)目標(biāo)器件庫的觸發(fā)器都包含異步復(fù)位端口,異步復(fù)位會(huì)節(jié)約邏輯資源。(2)異步復(fù)位設(shè)計(jì)簡(jiǎn)單。(3)對(duì)于多數(shù)FPGA,均有專用的全局異步復(fù)位/置位資源(GSR,GlobalSetReset),還可使用GSR資源,異步復(fù)位到達(dá)所有寄存器的偏斜最小。

異步復(fù)位的缺點(diǎn)如下:(1)異步復(fù)位的作用和釋放與時(shí)鐘沿并無直接關(guān)系,異步復(fù)位生效時(shí)問題并不明顯;但當(dāng)釋放異步復(fù)位時(shí),若異步復(fù)位信號(hào)釋放時(shí)間和時(shí)鐘的有效沿到達(dá)時(shí)間幾乎一致,則容易造成觸發(fā)器輸出為亞穩(wěn)態(tài),形成邏輯錯(cuò)誤。(2)若異步復(fù)位邏輯樹的組合邏輯產(chǎn)生了毛刺,則毛刺的有效沿會(huì)使觸發(fā)器誤復(fù)位,造成邏輯錯(cuò)誤。

2.3外部復(fù)位和內(nèi)部復(fù)位

外部復(fù)位,復(fù)位信號(hào)主要來自外部引腳的輸人。復(fù)位信號(hào)在電路板上可能會(huì)受到來自其他線路的串?dāng)_,因此可能產(chǎn)生毛刺,在無需復(fù)位系統(tǒng)時(shí),毛刺信號(hào)可能導(dǎo)致系統(tǒng)誤復(fù)位。

內(nèi)部復(fù)位,F(xiàn)PGA上電配置完成后,由FPGA內(nèi)部電路產(chǎn)生復(fù)位信號(hào),復(fù)位信號(hào)與時(shí)鐘同步。通常內(nèi)部復(fù)位的設(shè)計(jì)方法是:設(shè)計(jì)一個(gè)初始值為0X0000的SRL16,將其輸人接高電平,輸出作為復(fù)位信號(hào)。

3復(fù)位可靠性設(shè)計(jì)方法

3.1消除復(fù)位信號(hào)上的毛刺

在系統(tǒng)設(shè)計(jì)中,若采用低有效復(fù)位信號(hào),可按照?qǐng)D3所示方法對(duì)復(fù)位信號(hào)中的毛刺進(jìn)行消除。延時(shí)器件對(duì)數(shù)據(jù)進(jìn)行延時(shí)的長(zhǎng)度決定復(fù)位毛刺消除電路所能避免的毛刺長(zhǎng)度,而延時(shí)器件的延時(shí)長(zhǎng)度也決定需要提供有效復(fù)位信號(hào)的最短時(shí)間。

如果復(fù)位信號(hào)高有效,則將圖3中的或門改為與門使用。為更好地消除毛刺,可在復(fù)位毛刺消除電路后再加上寄存器對(duì)復(fù)位信號(hào)進(jìn)行時(shí)鐘同步。在通常復(fù)位電路的設(shè)計(jì)中,毛刺的長(zhǎng)度一般情況下>1個(gè)時(shí)鐘周期,<16個(gè)時(shí)鐘周期。為節(jié)省資源,延時(shí)器件通常選用SRL16。SRL16可設(shè)置初始值,但不帶復(fù)位功能16bit移位寄存器,能夠通過A0~A3的4根地在線選擇從第幾個(gè)寄存器輸出。通常將其作為一個(gè)普通的16bit移位寄存器使用。

[page]

3.2異步復(fù)位同步釋放

在有些應(yīng)用中,復(fù)位信號(hào)需要在時(shí)鐘尚未給出或不穩(wěn)定的情況下傳到后級(jí),在時(shí)鐘穩(wěn)定之后,再撤去復(fù)位信號(hào)。此時(shí)需使用異步復(fù)位來實(shí)現(xiàn)。由于異步復(fù)位時(shí),時(shí)鐘和復(fù)位關(guān)系的不確定性,易造成觸發(fā)器輸出亞穩(wěn)態(tài),引起邏輯錯(cuò)誤。為確保其復(fù)位的可靠性,通常采用異步復(fù)位,同步釋放的方式。

所謂異步復(fù)位,同步釋放就是在復(fù)位信號(hào)到達(dá)時(shí)不受時(shí)鐘信號(hào)的同步,而是在該信號(hào)釋放時(shí)受時(shí)鐘信號(hào)的同步。通過一個(gè)復(fù)位信號(hào)綜合器便可實(shí)現(xiàn)異步復(fù)位,同步釋放。綜合后的RTL圖如圖3所示,其仿真結(jié)果表明該電路能有效的實(shí)現(xiàn)復(fù)位及脫離復(fù)位。

圖3異步復(fù)位、同步釋放電路圖

3.3采用專用全局異步復(fù)位/置位資源

全局異步復(fù)位/置位資源的主要作用是對(duì)系統(tǒng)中存在的所有觸發(fā)器、鎖存器、查找表單元的輸出寄存器進(jìn)行復(fù)位,不會(huì)占有額外的布線資源。使用GSR資源,異步復(fù)位到達(dá)所有寄存器的偏斜最小。

3.4采用內(nèi)部復(fù)位的設(shè)計(jì)方法

在無需復(fù)位信號(hào)先于時(shí)鐘信號(hào)產(chǎn)生的應(yīng)用中,為避免外部復(fù)位毛刺的影響、異步復(fù)位電路可能引起的亞穩(wěn)態(tài)以及減少資源的使用率,可通過FPGA產(chǎn)生內(nèi)部復(fù)位,然后采用異步的方式對(duì)其的內(nèi)寄存器進(jìn)行復(fù)位。由于該復(fù)位信號(hào)由FPGA內(nèi)部產(chǎn)生,不會(huì)因外部干擾而產(chǎn)生毛刺,同時(shí)又與時(shí)鐘同步,不存在因異步復(fù)位導(dǎo)致的亞穩(wěn)態(tài)現(xiàn)象,因此可確保系統(tǒng)可靠復(fù)位。

4結(jié)束語

FPGA的可靠復(fù)位是保證系統(tǒng)能夠正常工作的必要條件,本文對(duì)FPGA設(shè)計(jì)中常用的復(fù)位設(shè)計(jì)方法進(jìn)行了分類、分析和比較,并針對(duì)各種復(fù)位方式的特點(diǎn),提出了如何提高復(fù)位設(shè)計(jì)可靠性的方法。在工程實(shí)踐中,上述方法可以有效減少或消除FPGA復(fù)位所產(chǎn)生的錯(cuò)誤。