【導(dǎo)讀】本文深入細(xì)致地分析了DSP控制系統(tǒng)的信號(hào)完整性問題,從PCB設(shè)計(jì)和軟件設(shè)計(jì)兩方面,提出電磁兼容性設(shè)計(jì)的方案。在教學(xué)過程中增加該實(shí)例的講解, 使得抽象的電磁兼容理論具體化。這樣,學(xué)生的知識(shí)面得到擴(kuò)展,對(duì)電磁兼容理論的理解會(huì)更加透徹,電磁兼容性設(shè)計(jì)的能力也會(huì)相應(yīng)提高。

電磁兼容EMC是電子、電氣設(shè)備或系統(tǒng)的一種重要技術(shù)性能。所謂電磁兼容性是指設(shè)備或系統(tǒng)能在所處的電磁環(huán)境中正常工作,同時(shí)又不對(duì)該環(huán)境中的其他任何事物構(gòu)成干擾的能力。

基于DSP的控制系統(tǒng)是一個(gè)高速復(fù)雜的數(shù)?;旌舷到y(tǒng),在工業(yè)過程中會(huì)受到各種干擾,使得系統(tǒng)不能正常運(yùn)行。同時(shí),DSP系統(tǒng)又不可避免地向外輻射電磁波,對(duì)周圍的電子設(shè)備產(chǎn)生干擾。因此,抑制系統(tǒng)的電磁干擾,提高系統(tǒng)電磁兼容性,成為設(shè)計(jì)DSP控制系統(tǒng)必須考慮的因素[1]。筆者在教學(xué)中發(fā)現(xiàn),學(xué)生對(duì)EMC的理解不夠透徹,對(duì)EMC設(shè)計(jì)了解太少。本文旨在通過對(duì)DSP控制系統(tǒng)中EMC設(shè)計(jì)實(shí)例的分析,加深學(xué)生對(duì)電磁兼容技術(shù)的理解。

1 電磁兼容技術(shù)

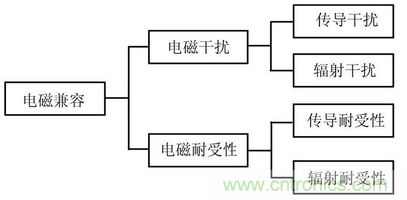

電磁兼容主要包括兩方面內(nèi)容:電磁干擾EMI和電磁耐受性EMS,如圖1所示。從圖1可以看出,電磁兼容問題主要從傳導(dǎo)和輻射兩方面進(jìn)行分析。電子系統(tǒng)電磁兼容設(shè)計(jì)的目標(biāo)就是找到一種性價(jià)比最優(yōu)的方式,來降低受試設(shè)備[2]EUT對(duì)外發(fā)射的電磁干擾強(qiáng)度,并提高受試設(shè)備自身的電磁干擾耐受性。

圖1 電磁兼容基本內(nèi)容

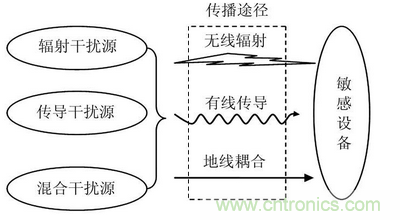

無論是復(fù)雜的系統(tǒng)還是簡單的電子元件,任何一個(gè)電磁干擾的產(chǎn)生都必須具備三要素[3]:電磁干擾源、傳播途徑和敏感設(shè)備。其傳播途徑包括無線輻射、有線傳導(dǎo)及地線耦合,如圖2所示。

圖2 電磁干擾三要素

上圖給出三要素之間的關(guān)系,電磁干擾源產(chǎn)生的電磁干擾,在一定條件下,通過一定的傳播途徑到達(dá)敏感設(shè)備,從而對(duì)敏感設(shè)備產(chǎn)生干擾。

為分析和設(shè)計(jì)電子系統(tǒng)或設(shè)備的電磁兼容性,必須分清這三要素。復(fù)雜的系統(tǒng)中干擾源和敏感設(shè)備間并沒有明顯的界線,很可能同時(shí)存在多個(gè)干擾源。干擾的傳播也會(huì)存在很多渠道,既有傳導(dǎo)耦合,也有輻射耦合。

2 高速電子系統(tǒng)的信號(hào)完整性

信號(hào)完整性是指?jìng)鬏數(shù)男盘?hào)質(zhì)量及信號(hào)定時(shí)的準(zhǔn)確性,即在要求的時(shí)間內(nèi)信號(hào)完整地從始端傳輸?shù)浇K端。信號(hào)完整性缺失不是由單一元素引起的,而是系統(tǒng)中的多個(gè)因素共同決定的。

在高速數(shù)字系統(tǒng)中,導(dǎo)線已不僅是單純的導(dǎo)體,而是一條具有分布參數(shù)的傳輸線。高速數(shù)字系統(tǒng)的信號(hào)互連較復(fù)雜,布線密度大。系統(tǒng)中各導(dǎo)體間的串?dāng)_、多電源間的干擾、D/A間的干擾等都成為影響信號(hào)完整性的因素。

3 DSP控制系統(tǒng)的電磁兼容性設(shè)計(jì)

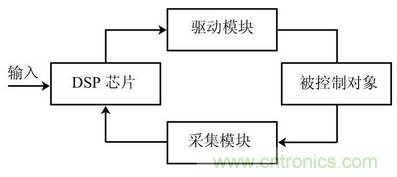

典型的DSP控制系統(tǒng)如圖3所示。該系統(tǒng)由DSP芯片(包括DSP控制核心、DSP片內(nèi)外設(shè)ADC模塊和I/O模塊等)、同DSP片內(nèi)外設(shè)I/O模塊相連的驅(qū)動(dòng)模塊、信號(hào)采集模塊以及被控制對(duì)象組成。

圖3 典型DSP控制系統(tǒng)

3.1 DSP控制系統(tǒng)的電磁干擾分析

DSP控制系統(tǒng)的電磁干擾信號(hào)會(huì)通過多種渠道進(jìn)入系統(tǒng),既可以以場(chǎng)的形式從空間耦合到系統(tǒng),也可以沿各種線路侵入系統(tǒng)。

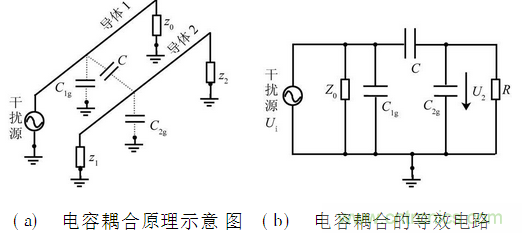

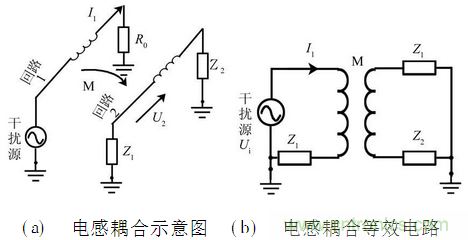

DSP控制系統(tǒng)的工作頻率較高,使得系統(tǒng)的中各分布電容和分布電感對(duì)系統(tǒng)的影響不可忽視。外界以及系統(tǒng)內(nèi)部間的信號(hào)可以通過導(dǎo)體間的分布電容和分布電感耦合到其他回路,耦合原理如圖4和圖5所示。

圖4 電容耦合原理

圖5 電感耦合原理

圖4所示導(dǎo)體1和導(dǎo)體2可以分別表示印刷電路板的時(shí)鐘線和數(shù)據(jù)線,兩導(dǎo)體對(duì)地都有分布電容C1g和C2g,兩導(dǎo)體之間有分布電容C。分布電容C

把兩導(dǎo)體連接在一個(gè)電路中,使得流經(jīng)兩導(dǎo)體的信號(hào)產(chǎn)生串?dāng)_。

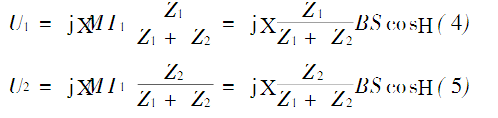

假設(shè)圖示的等效電路中,干擾源電壓為Ui,則其耦合到導(dǎo)體回路2中的電壓為

式中,X是Ui的角頻率;R是導(dǎo)體2的電阻值。

若R很小,且滿足

則

上式表明,在導(dǎo)體2低阻時(shí),電容耦合干擾只與兩導(dǎo)體間的耦合電容C有關(guān),在干擾源電壓和頻率恒定的情況下,我們可以通過導(dǎo)體的合適接地、屏蔽或隔離來減小C從而減小耦合電壓U2。

若R很大,且滿足

則有

上式表明在導(dǎo)體2高阻時(shí),電容耦合干擾不僅與導(dǎo)體間耦合電容C有關(guān),還與導(dǎo)體2對(duì)地的容C2g有關(guān)。

圖5表示回路1中有交變電流I1流過時(shí),產(chǎn)生的交變磁通通過回路2產(chǎn)生感應(yīng)電動(dòng)勢(shì),對(duì)回路2產(chǎn)生電磁干擾。

圖中干擾源I1在負(fù)載阻抗Z1和Z2上產(chǎn)生的干擾電壓分別為

式中,M為互感系數(shù),S為回路2的回路面積,B為角頻率為X的正弦磁通密度有效值,H為磁通與回路2的夾角。

由式(4)和式(5)可知,減小B、S和cosH可以減小電感耦合干擾。

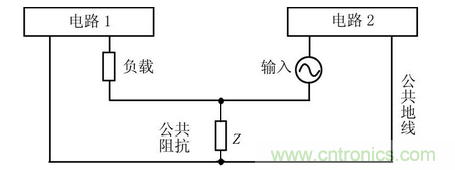

另外,系統(tǒng)內(nèi)部的數(shù)字電源和模擬電源引起的電磁干擾也非常嚴(yán)重。由于電源內(nèi)阻的存在,干擾信號(hào)都會(huì)通過電源內(nèi)阻或地耦合電阻形成互擾,即所謂的公共阻抗干擾[5],如圖6所示。

圖6 公共阻抗耦合

從圖6可知,電路1和電路2的電流流經(jīng)公共阻抗Z時(shí),在其上產(chǎn)生的壓降會(huì)使兩個(gè)電路彼此產(chǎn)生耦合,從而惡化系統(tǒng)的電磁兼容性。

3.2 DSP控制系統(tǒng)抗干擾設(shè)計(jì)

3.2.1合理設(shè)計(jì)PCB板減小系統(tǒng)串?dāng)_

串?dāng)_會(huì)隨著印刷電路板導(dǎo)線布局密度的增加越趨嚴(yán)重,在PCB設(shè)計(jì)中要盡量做到以下幾點(diǎn),以此減小串?dāng)_的影響。

(1)為防止外界干擾通過圖3所示的信號(hào)采集模塊進(jìn)入系統(tǒng),可采用某些器件對(duì)信號(hào)進(jìn)行隔離。

(2)為減小如圖4所示的兩相鄰導(dǎo)體間的互電容C,可在導(dǎo)體間加接地屏蔽通路,在PCB相鄰層上的布線要互相垂直,以防止層間的電容耦合。

(3)為改善電感耦合干擾,要盡量減小PCB中元件的物理尺寸、并行信號(hào)線的長度和信號(hào)線到地的參考距離間隔,或增大信號(hào)線間距。

(4)電路元件要遠(yuǎn)離I/O接口及易受干擾的區(qū)域,做到敏感器件(如模擬器件)、強(qiáng)干擾元件(如功率器件)和數(shù)字器件合理分開;讓電源線和地線單獨(dú)引出,在電源供給處匯集到一點(diǎn)。必要時(shí),加濾波器以隔離不同區(qū)域的噪聲。

(5)PCB布線時(shí)模擬電源引腳VCCA和VSSA要區(qū)別于數(shù)字電源引腳。采用單點(diǎn)接地,引腳的引線盡量短。

3.2.2 軟件設(shè)計(jì)減小DSP系統(tǒng)干擾

由于干擾的存在,DSP控制系統(tǒng)程序可能會(huì)跳轉(zhuǎn)到某些未知區(qū)域,導(dǎo)致程序跳轉(zhuǎn)錯(cuò)位。實(shí)際應(yīng)用中,我們可以采取以下措施來提高系統(tǒng)的電磁兼容性。

(1)在軟件的所有模塊設(shè)置看門狗,一旦軟件跳轉(zhuǎn)會(huì)自動(dòng)產(chǎn)生復(fù)位。

(2)對(duì)于輸入的開關(guān)信號(hào)進(jìn)行延時(shí)防抖動(dòng),并輔之硬件低通濾波。

(3)A/D轉(zhuǎn)換采用數(shù)字濾波,以防止突發(fā)性干擾。如采用平均法和比較平均法等。

(4)利用特有的外設(shè)控制字,設(shè)置合理的信號(hào)邊沿有效作用檢測(cè)時(shí)間。

推薦閱讀: