【導(dǎo)讀】本文分析討論了生長前氫氣蝕刻時間和缺陷密度之間的關(guān)系。事實上,透過發(fā)光致光和光分析方法,我們發(fā)現(xiàn)層錯形式的外延層缺陷和表面缺陷的數(shù)量隨蝕刻時間增加而增多。增加氫氣蝕刻時間后,襯底位錯變大,外延層缺陷數(shù)量增多。

碳化硅(SiC)在大功率、高溫、高頻等極端條件應(yīng)用領(lǐng)域具有很好的前景。但盡管商用4H-SiC單晶圓片的結(jié)晶完整性最近幾年顯著改進,這些晶圓的缺陷密度依然居高不下。經(jīng)研究證實,晶圓襯底的表面處理時間越長,則表面缺陷率也會跟著增加。

碳化硅(SiC)兼有寬能帶隙、高電擊穿場強、高熱導(dǎo)率、高載流子飽和速率等特性,在大功率、高溫、高頻等極端條件應(yīng)用領(lǐng)域具有很好的前景。盡管商用4H–SiC單晶圓片的結(jié)晶完整性最近幾年顯著改進,但這些晶圓的缺陷密度依然居高不下。

經(jīng)研究證實,晶圓襯底的表面處理時間越長,則表面缺陷率也會跟著增加。表面缺陷嚴(yán)重影響SiC元件品質(zhì)與矽元件相比,碳化硅的能帶隙更寬,本征載流子濃度更低,且在更高的溫度條件下仍能保持半導(dǎo)體特性,因此,采用碳化硅材料制成的元件,能在比矽元件更高的工作溫度運作。碳化硅的高電擊穿場強和高熱導(dǎo)率,結(jié)合高工作溫度,讓碳化硅元件取得極高的功率密度和能效。

如今,碳化硅晶圓品質(zhì)和元件制造制程顯著改進,各大半導(dǎo)體廠商紛紛展示了高壓碳化硅解決方案,其性能遠(yuǎn)超過矽蕭特基勢壘二極體(SBD)和場效應(yīng)電晶體(FET),其中包括阻斷電壓接近19kV的PiN整流管;擊穿電壓高于1.5kV的蕭特基二極體;擊穿電壓高達(dá)1.0kV的 MOSFET。

對于普通半導(dǎo)體技術(shù)特別是碳化硅元件,襯底材料的品質(zhì)極其重要。若在晶圓非均勻表面上有機械性紊亂區(qū)和氧化區(qū),使用這些晶圓制造出的半導(dǎo)體元件,其產(chǎn)品性能將會受到影響,例如重組率提高,或者在正常工作過程中出現(xiàn)無法預(yù)見的性能降低現(xiàn)象。商用碳化硅晶圓需要機械拋光處理,晶圓表面容易被刮傷,經(jīng)常看到晶圓上有大量的刮痕。

過去的研究報告證明,如果在外延層生長前正確處理襯底表面,晶圓襯底表面上的缺陷將會大幅減少,這是生長高品質(zhì)外延層的關(guān)鍵所在。我們知道,氫氣蝕刻方法可以去除數(shù)百奈米的體效應(yīng)材料,從而改善晶圓表面的缺陷問題。

S. Soubatch等科學(xué)家研究了在1,400~1,600℃溫度范圍內(nèi)氫氣氣相蝕刻方法對零偏4H-SiC(0001)晶圓的形貌和結(jié)構(gòu)的影響。在1,600℃高溫時,兩種不同的蝕刻缺陷比較常見,分別是在臺階流程式蝕刻期間形成的缺陷,以及結(jié)構(gòu)性蝕刻缺陷。

前者包含大階梯和全晶包高度臺階,后者則以螺型位錯為典型。最好的表面形貌是有一系列等距臺階的區(qū)域,生長在1,400℃。

C. Hallin等科學(xué)家研究了采用氫氣和氫丙烷蝕刻系統(tǒng)的4H-SiC和6H-SiC襯底表面原位制備方法。研究發(fā)現(xiàn),蝕刻后4H零偏表面更加不規(guī)則,有大臺階區(qū)和蝕坑,可能原因是在缺陷區(qū)蝕刻速率較高;與表面平行的微管和晶粒邊界變大,形成三角形蝕坑,表面滲有微管和其它位錯。然而,我們在4H氫氣蝕刻晶圓上看到更寬的帶狀缺陷,即層錯。透過在氫氣蝕刻流程增加丙烷,可以取得最佳的蝕刻條件,可去除刮痕而不留下任何矽滴痕跡。

該實驗研究了襯底表面的氫氣蝕刻時間對4H-SiC外延層缺陷的影響,同時還用AFM分析法研究蝕刻時間對外延層表面的影響。

表面處理時間與缺陷率呈正函數(shù)關(guān)系

本文利用一臺商用低壓力熱壁化學(xué)氣相沉積(LP-CVD)反應(yīng)器,將蝕刻時間擴至正常生產(chǎn)所用時間的三倍,觀察研究生長前蝕刻時間對同質(zhì)外延層的影響。經(jīng)過檢查與分析發(fā)現(xiàn),蝕刻時間與缺陷率之間關(guān)系明顯。此外,汞探針CV和FT-IR測量結(jié)果證明,摻雜和晶圓厚度均勻性也與蝕刻時間有關(guān)系。

該實驗使用反應(yīng)器完成同質(zhì)外延層生長,透過SiH4/C3H8系統(tǒng)分別供給矽和碳。載氣和外延層生長還原劑使用高純度工業(yè)級氫氣氣體;添加10%的氮氣氣體充當(dāng)摻雜劑。本實驗中使用的反應(yīng)器是東京威力科創(chuàng)出品的商用低壓力熱壁化學(xué)氣相沉積反應(yīng)器。在偏向方向4°的4H-SiC(0001)矽面n-型(~1018at/cm-3)襯底上,生長1E16 at/cm3 n-摻雜濃度的n-SiC外延層,以避免外延層上形成粗糙的馬賽克圖形。

本實驗針對中高壓二極體或MOSFET生長9.0微米薄膜外延層;操縱變因為蝕刻時間,分別使用二分之一參考蝕刻時間、參考蝕刻時間、兩倍參考蝕刻時間和三倍參考蝕刻時間來研究其外延層的研究生長過程;摻雜濃度為1E16 atm/cm3。

KLA-Tencor Candela CS920是一個晶圓表面缺陷檢查系統(tǒng),可以在一個單一檢測平臺上實現(xiàn)表面探測和光致發(fā)光(PL)技術(shù),用于檢測微蝕坑、蘿卜狀蝕坑、彗星狀蝕線、三角形蝕坑和層錯等表面缺陷。透過參數(shù)不同的通道之間的交叉相關(guān)(鐳射波長、表面角度、散射光幅度),實現(xiàn)巨集微缺陷檢測和自動分類。

汞探針電容電壓(Hg-CV)測量法用于評估摻雜濃度(從原級平臺到頂部直徑是17點)。摻雜濃度固定為1。

其他儀器方面,本實驗使用傅立葉變換紅外光譜儀(FT-IR)測量樣品厚度。表面分析實驗則使用Dimension 3100原子力顯微鏡(AFM)。顯微鏡為接觸測量模式,裝備一個單晶矽針尖。為取得更大的掃描區(qū)域,掃描尺寸是90×90μm2,掃描速率是1.0Hz。

生長過程中的層錯(SF)是比較常見的層內(nèi)缺陷,一般是在外延層生長初期開始成核(Nucleated),可能導(dǎo)致雙極元件的正向壓降變大?;嫖诲e(BPD)是蕭特基二極體層錯的核心,在雙極元件工作過程中擴大,導(dǎo)致雙極元件的正向特征變差。

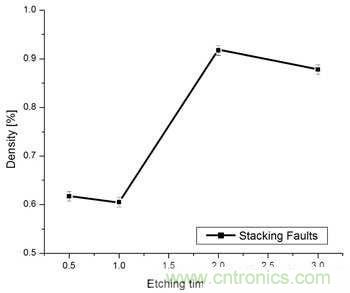

為了在化學(xué)機械拋光(CMP)后降低襯底表面粗糙度,氫氣表面蝕刻是生長過程中的一個關(guān)鍵程序,但是會放大襯底位錯現(xiàn)象。層錯密度是氫氣表面蝕刻時間的函數(shù),我們使用PL方法分析該參數(shù)的趨勢,如圖1所示,當(dāng)表面蝕刻時間是參考蝕刻時間的一半和三倍時,層錯密度從0.6%上升到0.9%。

圖1.層錯密度是蝕刻時間的函數(shù),隨蝕刻時間增加而上升。

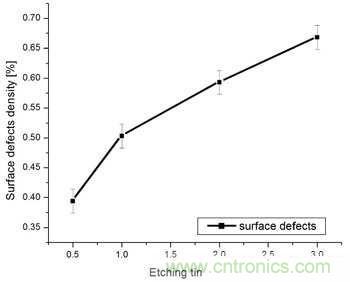

我們觀察到,表面缺陷密度與蝕刻時間具有相同的函數(shù)關(guān)系。如圖2所示,表面缺陷密度隨著氫氣蝕刻時間變長而升高。襯底表面蝕刻時間延長導(dǎo)致襯底位錯嚴(yán)重,結(jié)果在外延層出現(xiàn)更多的表面缺陷和層錯。

圖2.表面缺陷密度與蝕刻時間呈函數(shù)關(guān)系。

氫氣蝕刻連帶引發(fā)外延層缺陷 階褶密度明顯上升

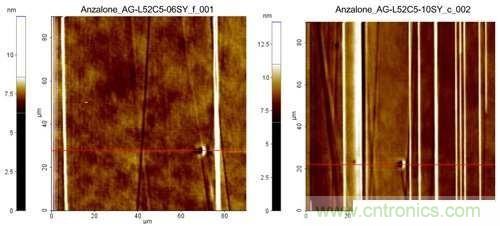

我們發(fā)現(xiàn),氫氣蝕刻制程可以改進表面形貌,但同時也在外延層上引起不同類型的微階褶(SB)和整體階褶現(xiàn)象。AFM表面粗糙度分析表明,階褶會影響對樣品表面均勻性。兩個樣品都顯示一個約6nm高、1μm寬的階褶。圖3顯示了x0.5(左圖)和x3(右圖)樣品在階褶密度上存在明顯差異。

圖3.不同蝕刻時間會在晶圓表面留下不同程度的階褶。圖左的蝕刻時間為二分之一參考時間,圖右為三倍參考時間。

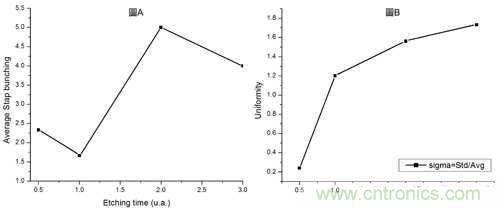

圖4a和圖4b分別描述了階褶數(shù)量和表面均勻度隨蝕刻時間增加而發(fā)生的變化。具體講,如圖4a所示,階褶是蝕刻時間的函數(shù),隨蝕刻時間增加而提高。測量值是在不同測量區(qū)的不同測量值的平均數(shù)。從這些測量值看,我們在晶圓上發(fā)現(xiàn)SB晶圓均勻性(Sigma/Mean)存在差異。透過延長蝕刻時間評估均勻性惡化,我們發(fā)現(xiàn)在x3樣品內(nèi)有高階褶密度區(qū),而x0.5樣品的均勻性更好(在每個被分析部分,大約有2個階褶)。

圖4.圖A為階褶數(shù)量與蝕刻時間的關(guān)系。圖B表面均勻度與蝕刻時間的關(guān)系。

本文分析討論了生長前氫氣蝕刻時間和缺陷密度之間的關(guān)系。事實上,透過發(fā)光致光和光分析方法,我們發(fā)現(xiàn)層錯形式的外延層缺陷和表面缺陷的數(shù)量隨蝕刻時間增加而增多。增加氫氣蝕刻時間后,襯底位錯變大,外延層缺陷數(shù)量增多。AFM分析結(jié)果顯示,階褶密度和均勻性會隨著氫氣表面蝕刻時間增加而提高。