【導(dǎo)讀】電源工程師都知道一個(gè)電路常識(shí):數(shù)字電路要運(yùn)行穩(wěn)定可靠,電源一定要”干凈“,并且能量補(bǔ)充一定要及時(shí),也就是濾波去耦一定要好。但是很多時(shí)候大家都是靠慣性和經(jīng)驗(yàn)來(lái)確定濾波電容容值,如何準(zhǔn)確的來(lái)確定濾波電容容值呢?

根據(jù)電路常識(shí),電源工程師都能夠明白,數(shù)字電路要運(yùn)行穩(wěn)定可靠,電源一定要”干凈“,并且能量補(bǔ)充一定要及時(shí),也就是濾波去耦一定要好。什么是濾波去耦,簡(jiǎn)單的說(shuō)就是在芯片不需要電流的時(shí)候存儲(chǔ)能量,在你需要電流的時(shí)候又能及時(shí)的補(bǔ)充能量。不要說(shuō)這個(gè)職責(zé)不是DCDC、LDO的嗎,這個(gè)在低頻的時(shí)候它們可以搞定,但高速的數(shù)字系統(tǒng)就不一樣了。

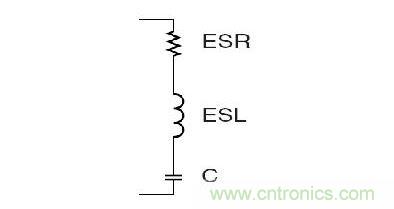

先來(lái)看看電容,電容的作用簡(jiǎn)單的說(shuō)就是存儲(chǔ)電荷。我們都知道在電源中要加電容濾波,在每個(gè)芯片的電源腳放置一個(gè)0.1uF的電容去耦。這些板子芯片的電源腳旁邊的電容是0.1uF的或者0.01uF的,有什么講究嗎。要搞懂這個(gè)就要了解電容的實(shí)際特性。理想的電容它只是一個(gè)電荷的存儲(chǔ)器,即C。而實(shí)際制造出來(lái)的電容卻不是那么簡(jiǎn)單,分析電源完整性的時(shí)候我們常用的電容模型如下圖所示。

電容模型

我們由圖可見ESR是電容的串聯(lián)等效電阻,ESL是電容的串聯(lián)等效電感,C才是真正的理想電容。ESR和ESL是由電容的制造工藝和材料決定的,沒法消除。那這兩個(gè)東西對(duì)電路有什么影響。ESR影響電源的紋波,ESL影響電容的濾波頻率特性。我們知道電容的容抗Zc=1/ωC,電感的感抗Zl=ωL,( ω=2πf),實(shí)際電容的復(fù)阻抗為:Z=ESR+jωL-1/jωC= ESR+j2πf L-1/j2πf C??梢姰?dāng)頻率很低的時(shí)候是電容起作用,而頻率高到一定的時(shí)候電感的作用就不可忽視了,再高的時(shí)候電感就起主導(dǎo)作用了。

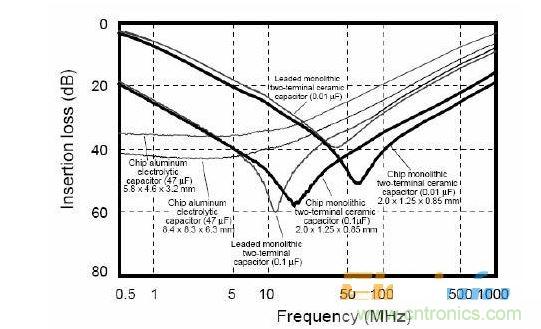

電容就失去濾波的作用了。所以記住,高頻的時(shí)候電容就不是單純的電容了。實(shí)際電容的濾波曲線如下圖所示。上面說(shuō)了電容的等效串聯(lián)電感是電容的制造工藝和材料決定的,實(shí)際的貼片陶瓷電容的ESL從零點(diǎn)幾nH到幾個(gè)nH,封裝越小ESL就越小。從上面電容的濾波曲線上我們還看出并不是平坦的,它像一個(gè)’V’,也就是說(shuō)有選頻特性,那時(shí)候我們希望它是越平越好(前級(jí)的板級(jí)濾波),而有時(shí)候希望它越越尖越好(濾波或陷波)。影響這個(gè)特性的是電容的品質(zhì)因素Q,Q=1/ωCESR,ESR越大,Q就越小,曲線就越平坦,反之ESR越小,Q就越大,曲線就越尖。

通常鉭電容和鋁電解有比較小的ESL,而ESR大,所以鉭電容和鋁電解具有很寬的有效頻率范圍,非常適合前級(jí)的板級(jí)濾波。也就是在DCDC或者LDO的輸入級(jí)常常用較大容量的鉭電容來(lái)濾波。而在靠近芯片的地方放一些10uF和0.1uF的電容來(lái)去耦,陶瓷電容有很低的ESR。說(shuō)了那么多,那到底我們?cè)诳拷酒墓苣_處放置0.1uF還是0.01uF,下面列出來(lái)給大家參考。

頻率范圍(HZ) 電容取值:DC-100K 10uF以上的鉭電容或鋁電解;100K-10M 100nF(0.1uF)陶瓷電容;10M-100M 10nF(0.01uF)陶瓷電容;>100M 1nF(0.001uF)陶瓷電容和PCB的地平面與電源平面的電容。

所以我們靠照抄和慣性都不能確定電路中的電容容值,經(jīng)過(guò)以上論證顯示我們?cè)谠O(shè)計(jì)電路的時(shí)候,不要見到什么都放0.1uF的電容,有些高速系統(tǒng)中這些0.1uF的電容根本就起不了作用。