【導(dǎo)讀】在半導(dǎo)體工藝中許多器件的重要參數(shù)和性能都與薄層電阻有關(guān),為提高厚、薄膜集成電路和片式電阻的生產(chǎn)精度,需要使用設(shè)備儀器如探針臺(tái)、激光調(diào)阻機(jī)對(duì)其進(jìn)行測(cè)試或修調(diào)。一般所用的測(cè)量儀器或設(shè)備都包含連接、激勵(lì)、測(cè)量和顯示單元,有時(shí)還有后期數(shù)據(jù)處理單元。

1、引 言

在半導(dǎo)體工藝中許多器件的重要參數(shù)和性能都與薄層電阻有關(guān),為提高厚、薄膜集成電路和片式電阻的生產(chǎn)精度,需要使用設(shè)備儀器如探針臺(tái)、激光調(diào)阻機(jī)對(duì)其進(jìn)行測(cè)試或修調(diào)。一般所用的測(cè)量儀器或設(shè)備都包含連接、激勵(lì)、測(cè)量和顯示單元,有時(shí)還有后期數(shù)據(jù)處理單元。采用不同的測(cè)量方法和不同的連接方式引入的測(cè)量誤差不同,得到的測(cè)量精度也不同。通常開關(guān)矩陣中繼電器觸點(diǎn)閉合電阻為1Ω左右,F(xiàn)ET開關(guān)打開時(shí)的電阻為十幾歐,引線電阻為幾百毫歐。如何根據(jù)需要減少測(cè)量誤差是測(cè)試技術(shù)的關(guān)鍵之一。

2、電阻測(cè)試基本原理

在電阻測(cè)試中我們常采用恒流測(cè)壓方法、惠斯通電橋(單臂電橋)和雙臂電橋方法。

2.1 恒流測(cè)壓方法

采用不同的測(cè)量方法和連接方式對(duì)電阻進(jìn)行有效測(cè)量

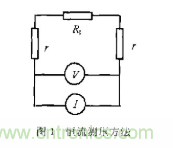

圖1中, r是引線電阻與接觸電阻之和;I是程控恒流電流源; V是具有極高輸入阻抗的電壓表,它對(duì)恒流電流源不產(chǎn)生分流作用。施加已知的恒定電流I,流過被測(cè)電阻R t,然后測(cè)量出電阻兩端的電壓V,當(dāng)R t>> r時(shí),根據(jù)公式Rt=V/ I就可算出電阻值。

2.2 惠斯通電橋方法

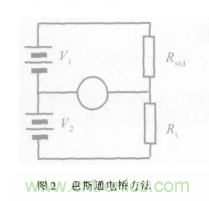

圖2中,V1,V 2是程控恒電壓源;Rstd是標(biāo)準(zhǔn)電阻; Rt是被測(cè)電阻;I是電流表。當(dāng)電橋平衡即流過電流表I的電流為零時(shí),有V1 /V2=Rstd/R t,由此可計(jì)算出Rt=R std×V2/V1 。

2.3 雙臂電橋方法

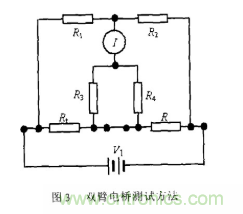

單臂電橋測(cè)量范圍為10~106 Ω,單電橋測(cè)幾歐姆的低電阻時(shí),引線電阻和接觸電阻已經(jīng)不可忽略。而雙臂電橋適用于10-6~102 Ω電阻的測(cè)量,它是改進(jìn)的單臂電橋,如圖3。將電橋中的中低電阻 Rt和R改成四端接法,并在橋路中增加兩個(gè)高阻電阻R3和R4,則大大降低了引線電阻和接觸電阻的影響。詳細(xì)介紹參見文獻(xiàn)[1]。

本文主要介紹恒流測(cè)壓法。當(dāng)被測(cè)電阻阻值遠(yuǎn)遠(yuǎn)大于測(cè)試引線電阻和測(cè)試探針與測(cè)試點(diǎn)的接觸電阻時(shí),采用圖1所示的兩線測(cè)試的基本方法是可行的,并且也可以獲得相當(dāng)高的測(cè)試精度。

3、開爾文連接測(cè)試技術(shù)

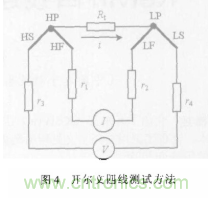

當(dāng)被測(cè)電阻阻值小于幾歐,測(cè)試引線的電阻和探針與測(cè)試點(diǎn)的接觸電阻與被測(cè)電阻相比已不能忽略不計(jì)時(shí),若仍采用兩線測(cè)試方法必將導(dǎo)致測(cè)試誤差增大。此時(shí)可采用開爾文連接方式(或稱四線測(cè)試方式)來進(jìn)行測(cè)試,如圖4。

開爾文連接有兩個(gè)要求:對(duì)于每個(gè)測(cè)試點(diǎn)都有一條激勵(lì)線F和一條檢測(cè)線S,二者嚴(yán)格分開,各自構(gòu)成獨(dú)立回路;同時(shí)要求S線必須接到一個(gè)有極高輸入阻抗的測(cè)試回路上,使流過檢測(cè)線S的電流極小,近似為零。

圖4中r表示引線電阻和探針與測(cè)試點(diǎn)的接觸電阻之和。由于流過測(cè)試回路的電流為零,在 r3,r4上的壓降也為零,而激勵(lì)電流 I在r1,r2上的壓降不影響I在被測(cè)電阻上的壓降,所以電壓表可以準(zhǔn)確測(cè)出 Rt兩端的電壓值,從而準(zhǔn)確測(cè)量出R t的阻值。測(cè)試結(jié)果和r無關(guān),有效地減小了測(cè)量誤差。

按照作用和電位的高低,這四條線分別被稱為高電位施加線(HF)、低電位施加線(LF)、高電位檢測(cè)線(HS)和低電位檢測(cè)線(LS)。

4、電阻隔離測(cè)試技術(shù)

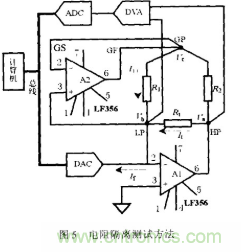

對(duì)于施加的恒定激勵(lì)電流能全部流過被測(cè)電阻的情況下,使用上述方法測(cè)試是很簡便的,比如測(cè)試單個(gè)電阻。但我們還常常遇到被測(cè)電阻與一個(gè)電阻網(wǎng)絡(luò)并聯(lián)的情況,這個(gè)電阻網(wǎng)絡(luò)會(huì)對(duì)施加電流有分流作用,導(dǎo)致無法采用上述方法進(jìn)行測(cè)試,在這種情況下我們必須采用電阻隔離測(cè)試技術(shù),其測(cè)試電路原理如圖5。

圖中,Rt是被測(cè)電阻, R1,R2串聯(lián)后再與 Rt并聯(lián);A1,A2是高輸入阻抗、高精度運(yùn)算放大器;DVA是高輸入阻抗、高精度差分電壓的程控放大倍數(shù)儀用放大器,它的輸出與數(shù)模轉(zhuǎn)換ADC相連;DAC是電流輸出型數(shù)模轉(zhuǎn)換器,DAC與A1構(gòu)成程控恒流源;根據(jù)計(jì)算機(jī)控制,DAC輸出不同的恒定電流If。

A2構(gòu)成電壓跟隨電路使Vc =Vb,從而I1=0。因此計(jì)算機(jī)通過16位電流輸出型DAC設(shè)定If 就控制了流過被測(cè)電阻Rt的電流I t,再通過由DVA和ADC構(gòu)成的電壓檢測(cè)電路測(cè)試出 Rt兩端的電壓就可算出Rt 的阻值。

這種方法等效于將R1 斷開,把被測(cè)電阻單獨(dú)隔離開來進(jìn)行測(cè)試的情況,因此稱其為電阻隔離測(cè)試技術(shù)。

5、分離開爾文連接測(cè)試電阻

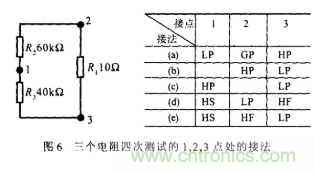

電阻隔離測(cè)試對(duì)絕大多數(shù)復(fù)雜電阻網(wǎng)絡(luò)都適用,但應(yīng)用到極少數(shù)電阻值比率極大的電阻網(wǎng)絡(luò)時(shí)就會(huì)產(chǎn)生一些問題。如圖6, R2/R1=6000,R 3/R1=4000,如果按圖5連接來測(cè)試電阻 R3時(shí)(即圖6-(a)連接),設(shè)施加電流 It為200μA,則在R3 兩端產(chǎn)生8V壓降,R2由于被隔離,其兩端電壓為零,所以在R1兩端必然產(chǎn)生8V電壓,導(dǎo)致 R2的功耗為 V2/R1=6.4W,這顯然是不允許的。如果把HP和LP 位置互換,由于A2不是理想器件,存在一定的失調(diào)電壓 Vos,即使小到20μV,在R1 上也會(huì)產(chǎn)生2μA的電流,使流過R3的電流產(chǎn)生1%的偏差,造成測(cè)試精度大大下降。

在這種情況下可以采用一種變形的開爾文連接方式來進(jìn)行測(cè)試,不再使用隔離方法。它仍采用四根線,但根據(jù)需要將其中一對(duì)或兩對(duì)F,S線分開接在不同的點(diǎn)上來進(jìn)行測(cè)試。這種方式稱為分離開爾文連接方式。本例中三個(gè)電阻要進(jìn)行四次測(cè)試才能計(jì)算出它們的阻值,四次測(cè)試的接法分別見圖6中的表,圖中1,2,3點(diǎn)為連接點(diǎn)。圖6-(b) 接法可直接測(cè)出R1的值;圖6-(c)可測(cè)出 R2與R3的并聯(lián)值R p;圖6-(d)和圖6-(e)分別測(cè)出阻值R2 ′和R3′。分析可知

R2′/R 3′=R2/R3 ,1/Rp=1/R2+1/ R3;由此可以解出R2 =Rp×(1+R2′/ R3′),R3=R 2×R3′/R2 ′。

在測(cè)試中還常常遇到被測(cè)電阻的兩端都沒有測(cè)試點(diǎn),隱藏在電阻網(wǎng)絡(luò)中的情況,如R-2R網(wǎng)絡(luò)。這時(shí)也需要使用分離開爾文連接來進(jìn)行測(cè)試。

6、 極小值電阻的測(cè)量技術(shù)

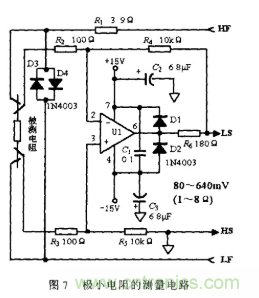

對(duì)于極小阻值范圍的電阻測(cè)量可以采用圖7所示電路完成,它可以測(cè)量10~ 80mΩ的電阻。通過差分運(yùn)算放大電路,把被測(cè)電阻產(chǎn)生的微弱電壓信號(hào)放大100倍,因此實(shí)際電阻值是測(cè)量值要除以100。圖中運(yùn)放UI采用低噪聲、高速、精密運(yùn)放,如OP-37EJ,AD645或MAX400。和高電位施加線(HF)串聯(lián)的電阻R1是用來匹配電流施加模塊的最佳輸出負(fù)載,R2到R5采用高精度高穩(wěn)定性的電阻來保證差放電路增益的穩(wěn)定,這決定了測(cè)量的精度和重復(fù)性。為了保證精度,對(duì)運(yùn)放的電源電壓要求很高,電路的安裝位置要盡可能靠近被測(cè)電阻,所有探頭要盡可能短,C2,C3要盡可能靠近運(yùn)放。

7、 結(jié)束語

由于自動(dòng)測(cè)試中要不斷地改變被測(cè)電阻,同時(shí)又要根據(jù)情況靈活地選擇測(cè)試方法和連接方式 ,因此實(shí)際生產(chǎn)中是使用探針卡將被測(cè)電路與系統(tǒng)相連,通過繼電器或FET開關(guān)組成的開關(guān)矩陳由軟件適當(dāng)切換來提高測(cè)試速度和生產(chǎn)效率。同時(shí)在不同的測(cè)量中探針采用不同的接法,如直線四探針法和方形四探針法,可克服各種因素的影響,優(yōu)化測(cè)量結(jié)果。如上所述,只要我們結(jié)合被測(cè)電阻的具體情況,靈活合理地應(yīng)用上面介紹的測(cè)試技術(shù),就可以得到滿意的測(cè)試結(jié)果。制造出高質(zhì)量的厚、薄膜集成電路和片式電阻來。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請(qǐng)電話或者郵箱聯(lián)系小編進(jìn)行侵刪。