【導讀】由于大多數工程師都在工程類院校專門學習過有關模數轉換器(ADC)、運算放大器(Op Amp)、數模轉換器(DAC)以及其他電子架構的課程,因此您可能會認為他們已理解了這些電路的所有基本功能。

數模轉換器均采用兩種基本架構,對其特性的了解將有助于為應用選擇正確的轉換器架構。

由于大多數工程師都在工程類院校專門學習過有關模數轉換器(ADC)、運算放大器(Op Amp)、數模轉換器(DAC)以及其他電子架構的課程,因此您可能會認為他們已理解了這些電路的所有基本功能。大多數人都對 ADC 的工作原理有了一個很好的了解,但是對 DAC 的工作原理卻不太熟悉,它究竟有何功能呢?

同樣,對于大多數人來說,DAC 只不過是一個輸入端為數字信號數據而輸出端為模擬信號數據的“黑匣子”。只有為數不多的人知道其在架構方面的區(qū)別,以及與 R2R 梯形架構相比一個電阻串架構所具有的優(yōu)點和缺點。了解他們之間的不同之處并了解這些通用 DAC 的工作原理可以使設計人員為其應用選擇最佳的 DAC。本文將對 DAC 的基本工作原理進行闡述,并對您一直想知道的一些問題做出解答。

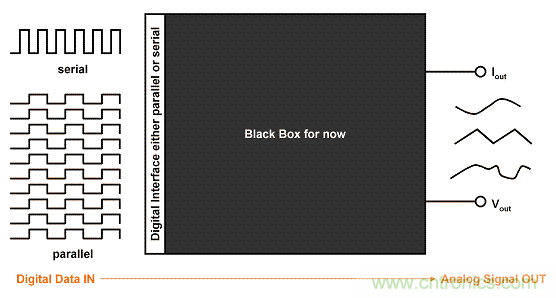

盡管 DAC 通常被視為一個輸入端為數字信號數據而輸出端為模擬信號數據的“黑匣子”,但卻內藏玄機。數字數據可以是串行數據格式也可以是并行數據格式。像 SPI 或 I2C 之類串行傳輸數字數據流的接口,就像是一條條進入“黑匣子”的項鏈或鏈條,而并行接口會在一個時鐘周期內將所有必要的比特加載到該器件中。與該器件的另一側,模擬輸出信號可以是一個電壓或一個電流,如圖1 所示。

圖1 數模轉換器的主要功能

不同的輸入接口所提供的數據格式也有所不同,所以在速度、引腳數量、芯片面積、器件尺寸以及靈活性上都有很大的不同。但是,串行和并行接口均能將數字數據輸入到該器件中。

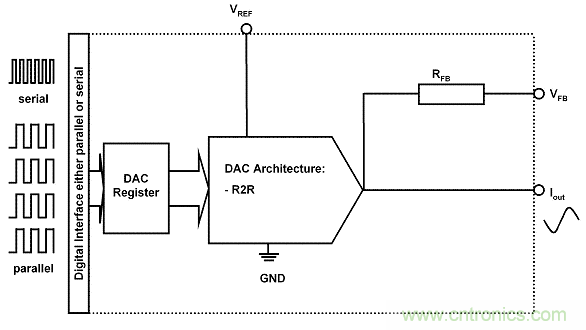

一旦數字數據被輸入到黑匣子(第一個功能塊),那么輸入寄存器就會像串行-并行轉換那樣工作,或者在多通道器件中對該數據進行存儲,直到該數據被傳輸至單個 DAC 寄存器中。在輸入寄存器和 DAC 架構之間起連接作用的 DAC 寄存器將起到一個存儲器的作用,并對數字數據加以存儲。

在 DAC 設計之初,該 DAC 寄存器為一個保存數字數據的外部存儲器。如果沒有 該 DAC 寄存器,那么由于模擬電路的實時饋入,DAC 的輸出將隨著外部輸入總線的任何變化而立即發(fā)生變化。在用戶決定用新代碼更新 DAC 寄存器之前,該數據會一直駐留在 DAC 寄存器之中。DAC 寄存器主要起到了一個觸發(fā)電路的作用。

圖2:基本功能模塊架構

當今的高精度 DAC 主要采用了兩種架構:R2R 架構和電阻串架構。這兩種架構均為采用了一些數字控制邏輯的模擬電路。通過一款基本的 R2R 架構,就有可能生成一個電流輸出或電壓輸出;而電阻串架構只能利用一個輸出緩沖器生成一個電壓輸出,如圖2 中的輸出電路結構圖所示。在電流輸出的情況下,沒有實施輸出緩沖器。

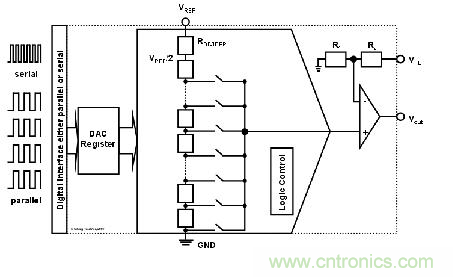

電阻串架構

顧名思義,電阻串架構就是一個以串聯形式放置的一串電阻,以構建一個電阻串。從理論上來說,您可能會需要 256 個電阻才能構建一款 8 位 DAC(28 = 256)(請參見圖3 ),包括產生一個電壓輸出的內部輸出緩沖器,該電壓輸出同數字輸入代碼等效。

圖3 主要的電壓輸出電阻串架構

提高精度也就是說要增加所需電阻的數量以構建一個電阻串 DAC。對于一款 16 位DAC 而言,可能需要65,536 個電阻才能生成所有可能的電壓/數字階躍(step)。但是,在現實真正的設計中,在一顆芯片上實施近 66,000 個電阻是不切實際的,對于當今的小封裝,低功耗和低成本要求而言尤為如此。

因此,設計人員推出了其他更小的電路設計方案,如可降低電阻串上所需電阻數量以及接觸點的內插式放大器,從而實現了功耗更低且更節(jié)省空間的設計。該內插式放大器用來代替輸出緩沖器。當今的一些電阻串架構擁有一個可用作放大器外部反饋環(huán)路的引腳。

由于特定的電阻串架構,電阻串 DAC 具有低成本和保證單調性能的優(yōu)點。值得一提的另外一個很重要的優(yōu)點是可以實現小型封裝的低功耗和小裸片面積,從而使他們非常適合便攜式應用。其另外一個優(yōu)點是輸出緩沖器已經包括在該架構之中,從而無需使用更多的板上外部組件。

其次,該輸出緩沖器還實現了內部電阻和模擬電路與外界的隔離,這在低阻抗電路中非常有用。許多應用都要求低突波能量,這也是電阻串架構的另外一個優(yōu)點。

另一方面,由于電阻串設計的更高阻抗,所以其噪聲通常會高于 R2R 架構的噪聲。設計人員還應該清楚地知道有限的精度(亦稱為積分非線性(INL))。較早的設計通常在中-60 最低位(LSB)提供 INL 數字,而較新型的一些設計則利用改進的工藝技術,現在可以在 4LSB 區(qū)域提供典型的 INL 數字。對于諸如馬達控制或過程控制的許多閉環(huán)應用而言,一個典型的 4 LSB INL 就已經足夠了。然而,對于其他應用而言(如:自動測試設備),這還遠遠不夠,那些應用通常需要1 LSB INL。因此,就有了另外一種不同的架構:R2R 架構。

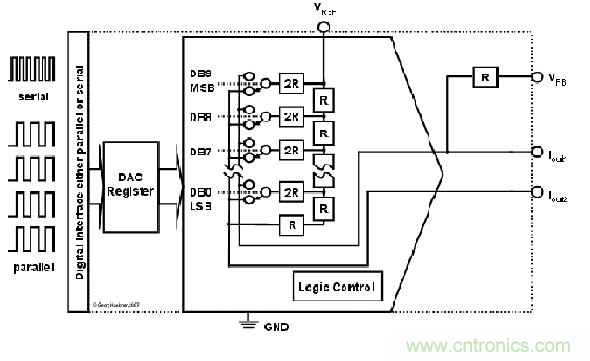

R2R 架構

R2R 架構主要是由形成一個電阻梯形的并聯電阻組成。圖4 顯示了一種可能的 R2R 梯形,這是一款乘法 DAC(MDAC),其 R2R 梯形的頂部與外部參考電壓相連。該架構可以輸出一個相當于數字輸入代碼的電流。

圖4 主要的電流輸出 R2R 架構

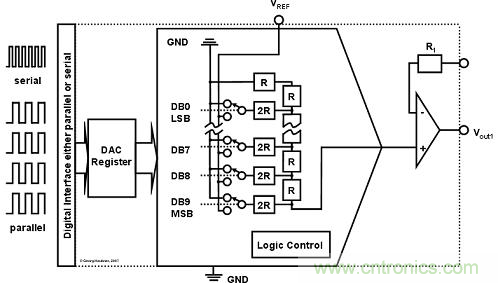

在硅片中實施一個 R2R 梯形的另一種方法如圖5 所示。

圖5 主要的電壓輸出 R2R 架構

其外部參考電壓沒有和 R2R梯形直接連接。根據不同的數字輸入代碼,開關將通過 R2R 網絡把參考電壓或接地電平連接至輸出緩沖器,該輸出緩沖器將所生成的電壓信號轉換成輸出電壓。

圖5 所示的架構只允許從 0V 到應用外部參考電壓的單極輸出電壓(請注意,DAC 的電源電壓必須等于或高于參考電壓)。通過將接地電平連接至一個額外的外部負參考電壓可以對后來提及的架構進行修改,而通過修改該架構則可以實現雙極運行。

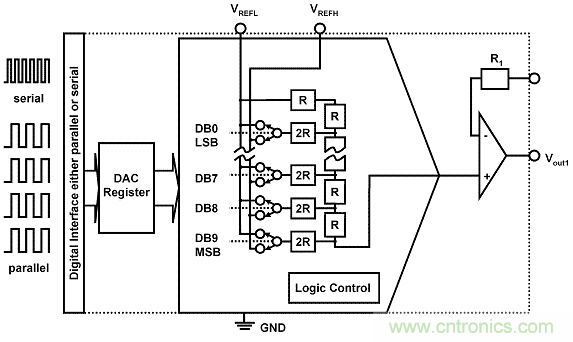

圖6 顯示了修改后的架構。

圖6 主要的雙極 R2R 架構

此種類型的架構還可用于選擇靈活的參考電壓。雖然 VREFL 可以為負電壓,但不需要讓其為負電壓。但是,VREFL 必須要低于 VREFH。詳盡的描述與參數請參見現有的產品說明書,如:DAC7714(見參考書目1)。

R2R DAC 具有低噪聲和高精度的優(yōu)點,其可能會提供 ±1 LSB INL 的卓越精度和DNL 性能。而且,該架構可實現高電壓輸出,MDAC 擁有較快的建立時間(小于 0.3 μsec),以及大于 10 MHz 的乘法帶寬。一般而言,其他 R2R 拓撲結構僅擁有中等的建立時間性能。

對于更寬泛的應用范圍(如數控校驗或工業(yè)可編程邏輯控制(PLC))而言,MDAC 為設計人員在選擇使用外部輸出緩沖器方面的靈活性使該架構類型更為有用。設計人員可以為特定的應用挑選最佳的運算放大器。另一方面,對于板上器件數量不斷增加的低阻抗連接而言,需要一個外部緩沖器。其次,與 R2R 架構相比,突波能量當然更適合電阻串架構,因此,對于波形生成和其他突波能量敏感型應用而言,很少采用 R2R DAC。

結論

我們不但要考慮諸如增益誤差或偏移誤差等其他電氣規(guī)范,而且還要考慮隨著溫度變化而發(fā)生的漂移或滿量程誤差等重要的參數,這些參數通常與具體的架構無關。為了有一個良好的開端,設計人員應首先查看基本要求并問問自己對最低精度和線性度有何要求。如果是在閉環(huán)應用中,那么一款較低成本且線性較差的電阻串 DAC 就足夠了;而如果是在開環(huán)應用中,則 R2R 架構在提供更佳的線性度和更高的精度方面就顯得更加出色。