【導(dǎo)讀】輸出電壓波形中除了開(kāi)關(guān)頻率分量的紋波以外,還存在高頻噪聲分量�,如圖1所示。高頻噪聲是如何形成的呢?主要是由電路中的寄生參數(shù)造成的�����。在實(shí)際電路中�����,PCB走線存在寄生電感和電阻��,輸入輸出電容會(huì)引入寄生電感和電阻����,兩個(gè)不同電位的平面之間會(huì)形成寄生電容�。

第一部分:輸出電壓噪聲

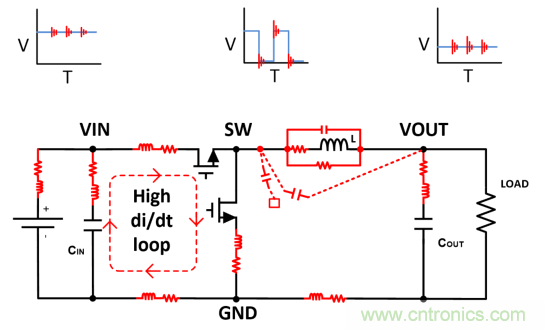

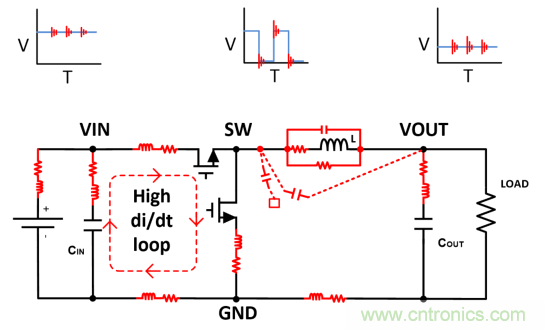

輸出電壓波形中除了開(kāi)關(guān)頻率分量的紋波以外,還存在高頻噪聲分量��,如圖1所示���。高頻噪聲是如何形成的呢�?主要是由電路中的寄生參數(shù)造成的����。在實(shí)際電路中,PCB走線存在寄生電感和電阻,輸入輸出電容會(huì)引入寄生電感和電阻��,兩個(gè)不同電位的平面之間會(huì)形成寄生電容����。以Buck電路為例,上下管切換的瞬間����,輸入回路中的寄生電感與開(kāi)關(guān)管的輸出電容諧振。因此��,開(kāi)關(guān)節(jié)點(diǎn)SW在上升和下降沿會(huì)產(chǎn)生高頻振蕩�����,且寄生參數(shù)越大��,振蕩的幅度也越大��,甚至損壞開(kāi)關(guān)管�。該高頻振蕩會(huì)通過(guò)SW節(jié)點(diǎn)與輸出VOUT之間的寄生電容耦合到輸出電壓,也就是輸出電壓中的高頻噪聲���。

圖1. Buck電路的寄生參數(shù)

第二部分:輸出電壓噪聲的抑制

了解高頻噪聲的來(lái)源和耦合途徑��,可以幫助我們有針對(duì)性地抑制輸出電壓噪聲�����。下面分別介紹如何通過(guò)噪聲源和耦合途徑來(lái)抑制輸出電壓噪聲��。

針對(duì)噪聲源��,有如下幾種抑制方法:

PCB布板時(shí)盡量減小輸入高di/dt回路

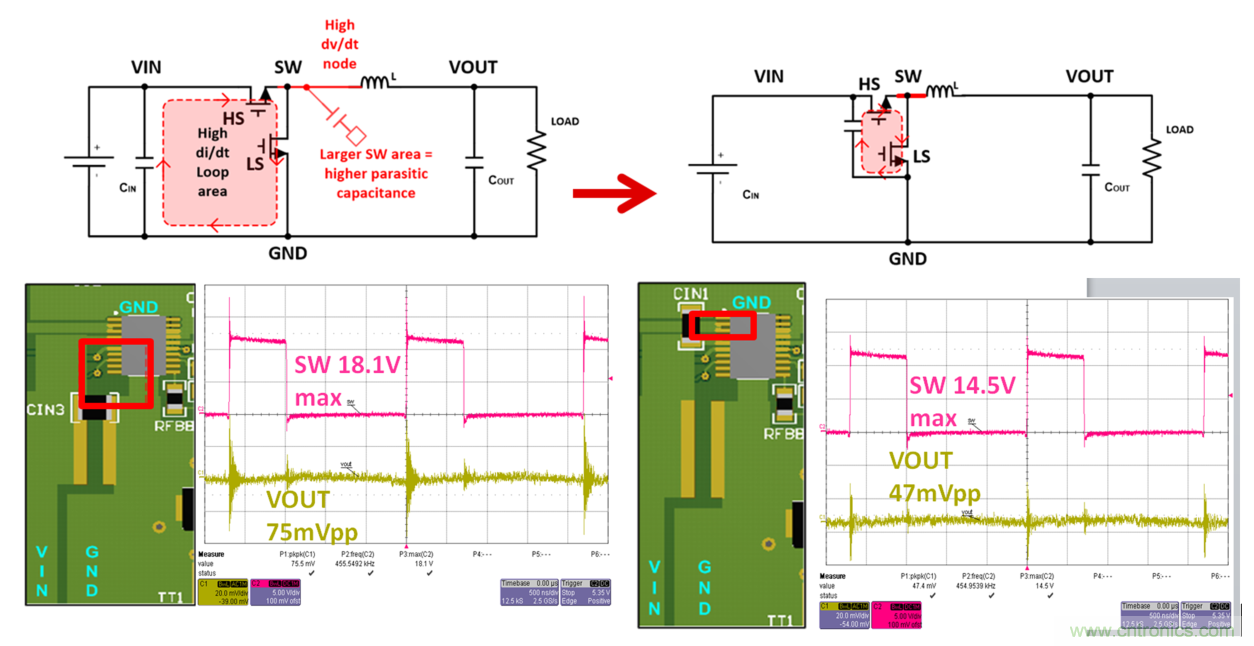

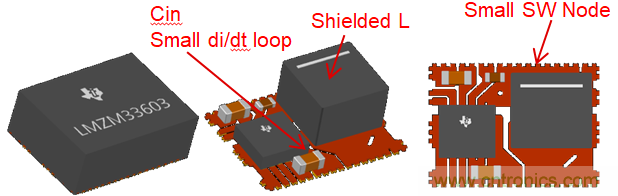

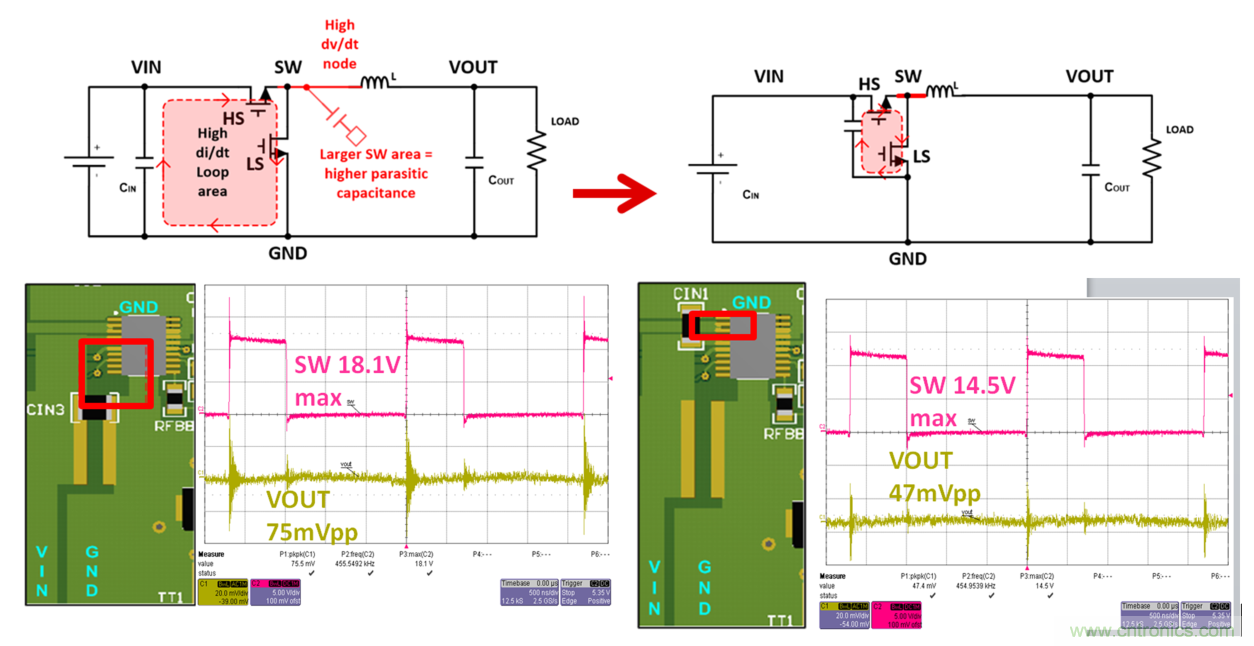

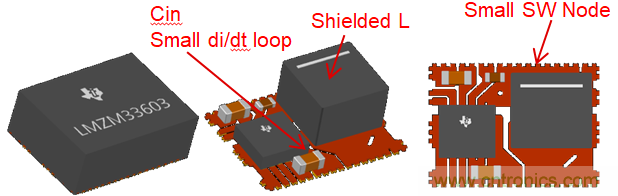

Buck電路的輸入回路由輸入電容CIN, 上管HS和下管LS組成��。 HS和LS的開(kāi)關(guān)動(dòng)作導(dǎo)致輸入環(huán)路電流的非連續(xù)性���,引起SW電壓的振蕩。 輸入環(huán)路越大����,振蕩越嚴(yán)重,開(kāi)關(guān)管的電壓應(yīng)力越大����。將輸入電容盡可能靠近HS和LS,保證輸入環(huán)路盡最小�����,可有效降低開(kāi)關(guān)節(jié)點(diǎn)SW的振蕩,如圖2所示�����。

圖2. 輸入電容位置對(duì)輸出電壓噪聲的影響

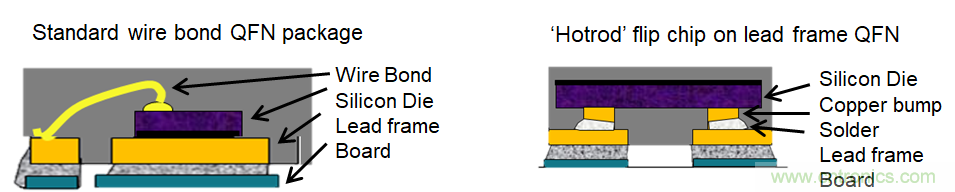

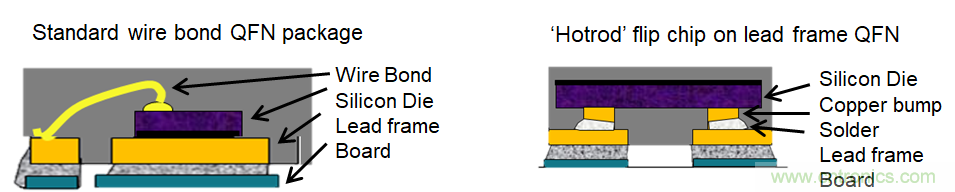

使用TI HotRod 封裝產(chǎn)品

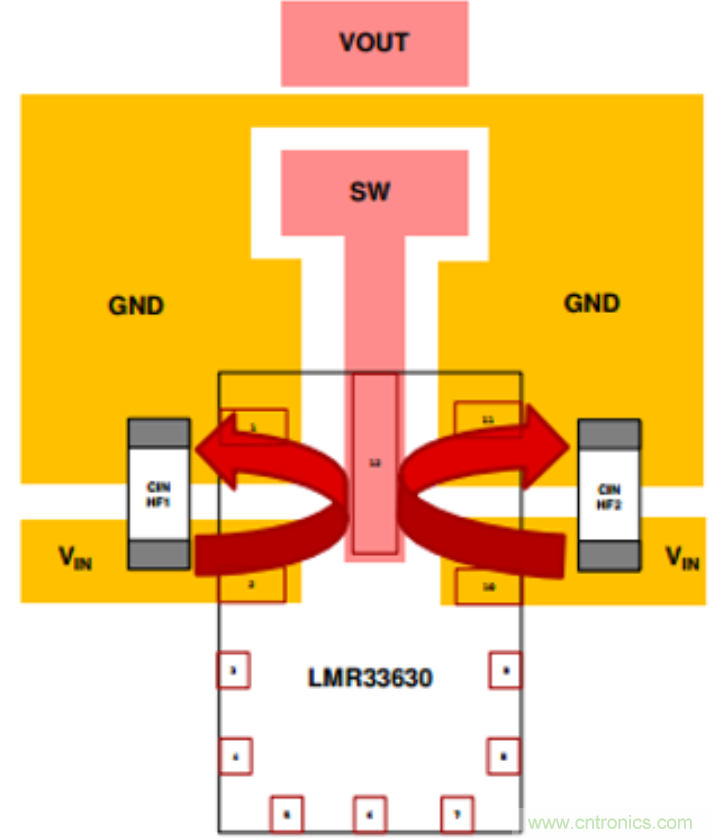

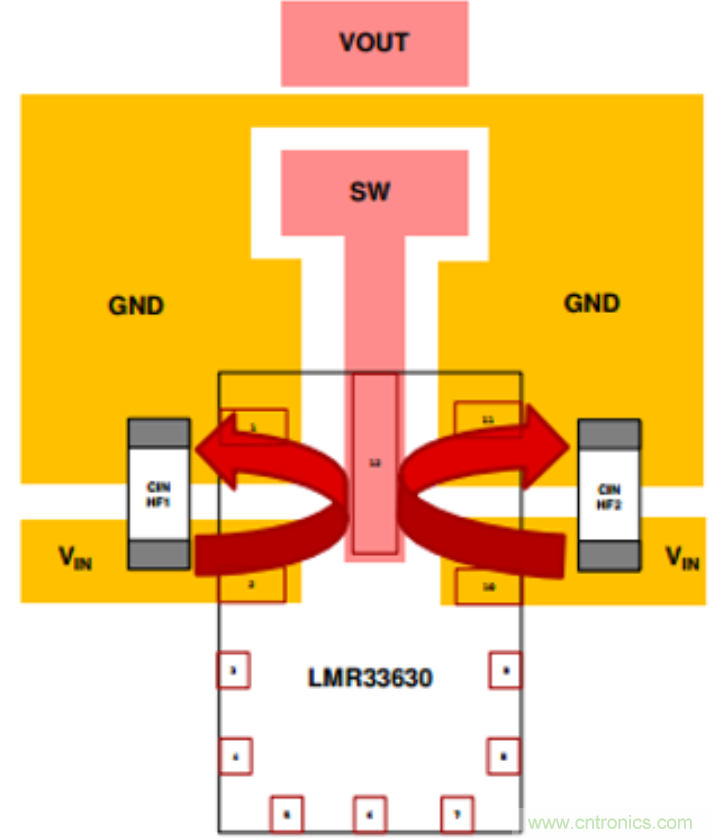

HotRod 封裝技術(shù)將芯片內(nèi)部的die倒置����,通過(guò)銅柱直接連接die 和lead frame,消除了使用wire bond引入的寄生電感��,減小SW節(jié)點(diǎn)的振蕩��,例如LMR33630�。另外,如圖4所示����,HotRod封裝有兩個(gè)電源VIN引腳和兩個(gè)接地GND引腳,分別位于封裝的兩端�。這種引腳分配可以減少VIN和GND回路造成的寄生環(huán)路電感。如果在器件的兩邊都有對(duì)稱(chēng)布局的輸入電容�,等效寄生回路電感則會(huì)減半(兩個(gè)相等的并聯(lián)電感)。這可以有效地減少高的di/dt 產(chǎn)生的噪聲���,相當(dāng)于高頻濾波�����。

圖3. TI Hotrod 封裝技術(shù)

圖4. LMR33630 對(duì)稱(chēng)輸入降低

1. 使用TI電源模塊產(chǎn)品

由于Layout的限制��,輸入電容無(wú)法無(wú)限靠近Buck 芯片��。TI的電源模塊產(chǎn)品集成高頻輸入電容和電感����,進(jìn)一步減小輸入回路和SW節(jié)點(diǎn)的面積��,降低噪聲�����,如圖5所示��。

圖5. TI電源模塊產(chǎn)品

針對(duì)耦合途徑����,有如下幾種抑制方法:

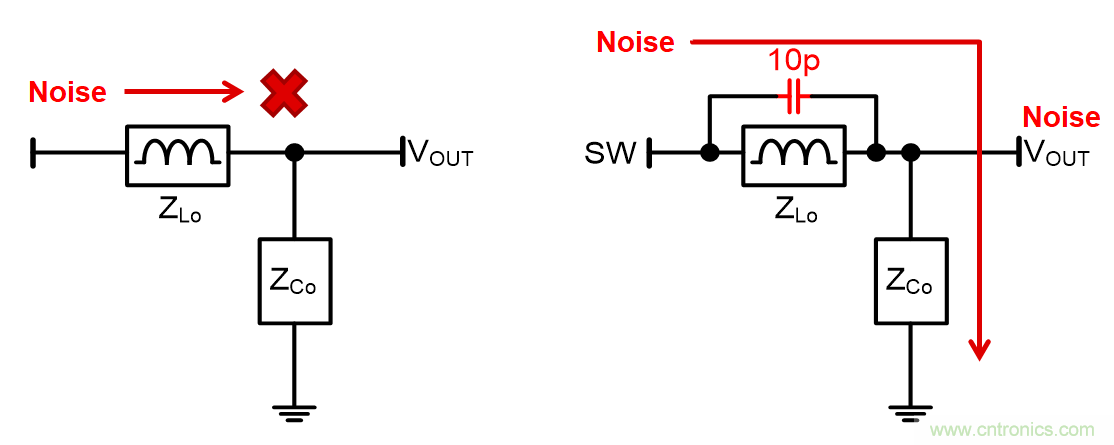

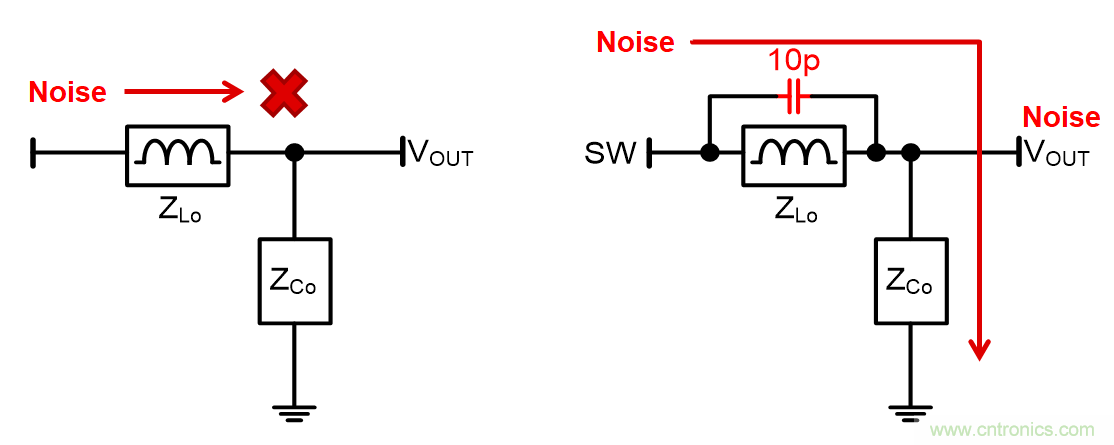

1. 選擇寄生電容較小的電感

理想電感對(duì)高頻噪聲呈現(xiàn)很大的阻抗,因此輸出電壓中的噪聲很小�。但是,實(shí)際電感存在寄生電容���,噪聲會(huì)通過(guò)耦合電容��,耦合到輸出電壓�����。因此��,選擇耦合電容較小的電感�����,在一定程度上可抑制輸出電壓噪聲�。

圖6.噪聲耦合途徑

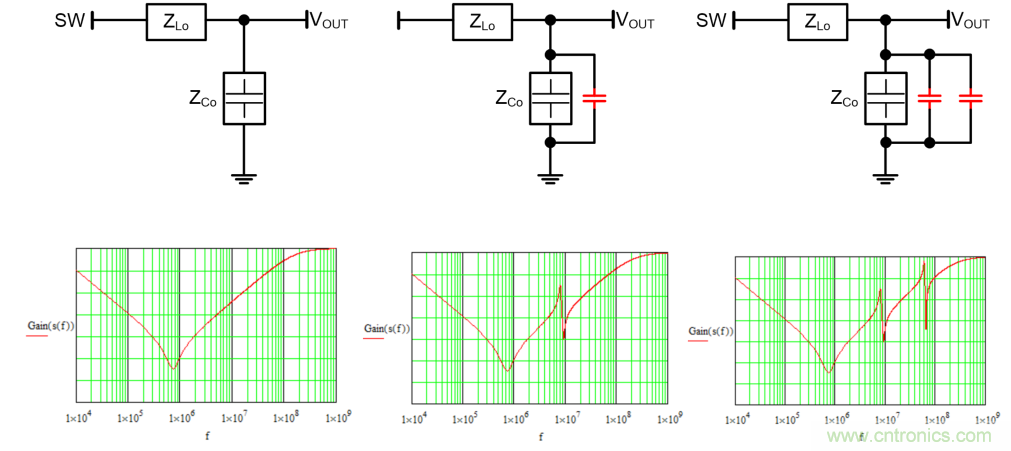

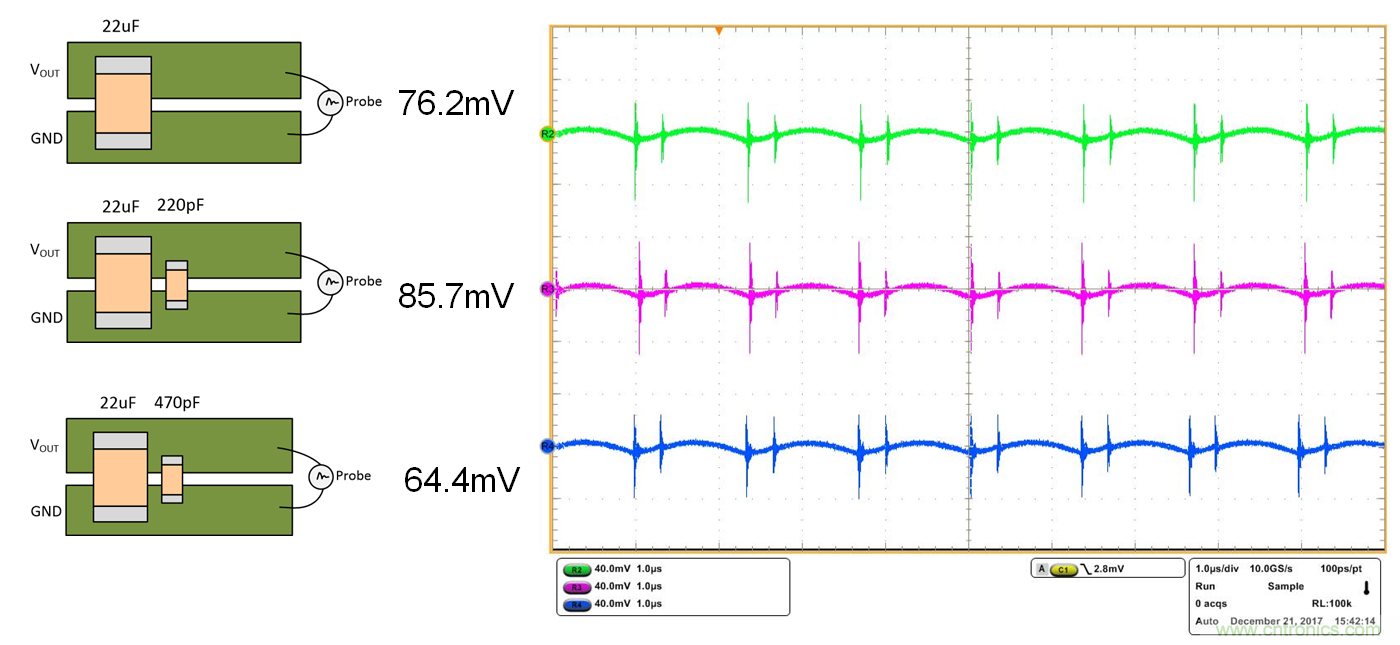

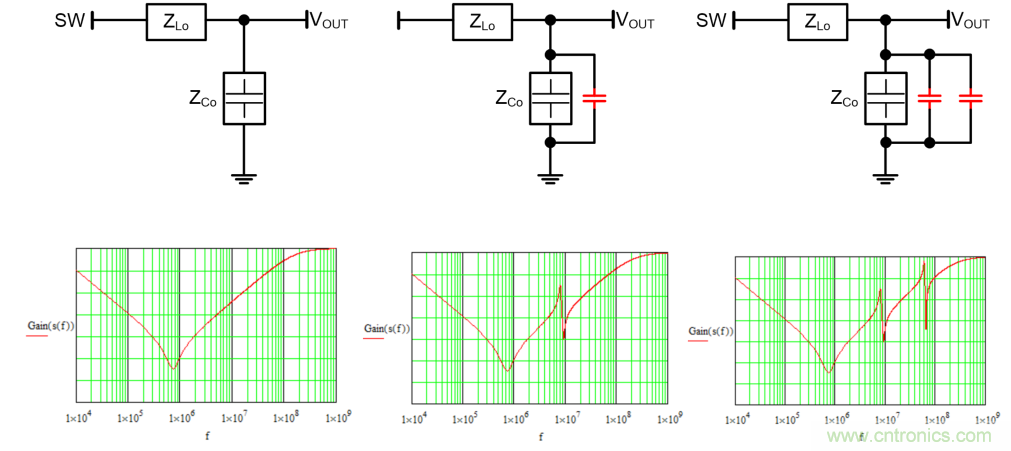

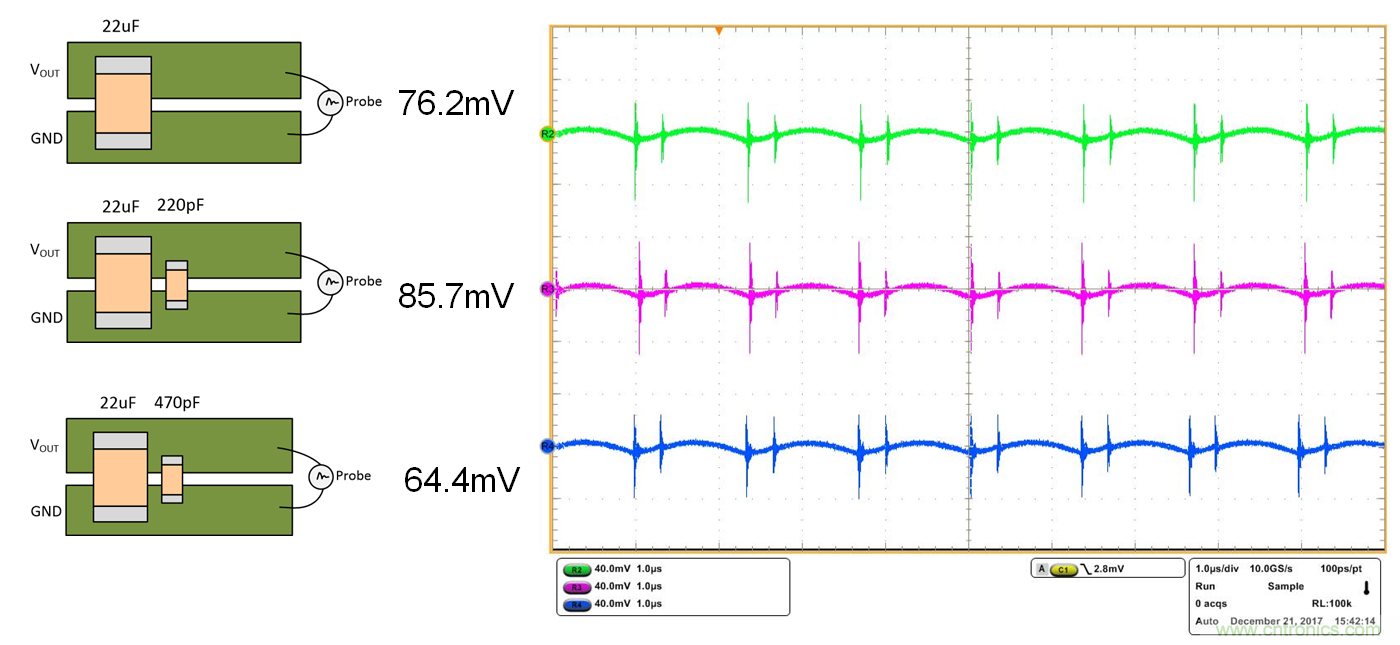

1. 并聯(lián)高頻濾波電容

直觀地理解,輸出電壓噪聲等于SW噪聲在輸出電容阻抗和輸出電感阻抗的分壓��。也就是說(shuō)�����,輸出電容在噪聲頻率處的阻抗越小���,耦合到輸出的噪聲就越小��。但是���,多個(gè)電容并聯(lián)后�����,輸出電容的阻抗曲線會(huì)存在多個(gè)諧振點(diǎn)����。如圖7所示����,增加高頻電容后,在諧振點(diǎn)處��,阻抗最小; 諧振點(diǎn)之前��,阻抗變大; 諧振點(diǎn)之后���,阻抗變小。因此�,并非增加高頻電容就一定能減小輸出噪聲。噪聲頻率位于諧振點(diǎn)處���,輸出噪聲最小�����。如圖8所示����,增加220pF的電容,電壓噪聲反而增加了�����。因此�����,選擇合適的輸出電容至關(guān)重要��。

圖7.輸出并聯(lián)高頻濾波電容的阻抗特性

圖8. 不同電容對(duì)輸出電壓噪聲的影響

綜上所述����,理解輸出電壓噪聲的形成原理,根據(jù)實(shí)際應(yīng)用要求��,選擇先進(jìn)的封裝技術(shù)/電源模塊產(chǎn)品��、優(yōu)化PCB布局�、增加濾波電容可有效降低輸出電壓噪聲���,滿(mǎn)足應(yīng)用需求。

推薦閱讀: