【導讀】在射頻超外差接收機中,下變頻器是一種常用的功能組件,主要用于射頻信號的偵測接收。針對 6 ~18 GHz 頻段,提出一種下變頻器的設計方案。下變頻器采用混合集成電路工藝,中頻處理帶寬1 GHz,噪聲系數(shù)優(yōu)于6 dB,幅度一致性優(yōu)于±2 dB,相位一致性優(yōu)于±15°,無虛假動態(tài)范圍大于50 dB。組件內(nèi)部采用多功能芯片和 MEMS濾波器組,內(nèi)置多級數(shù)控衰減和數(shù)控移相器。下變頻器具有頻段寬、體積小、集成度高、易于調(diào)試的優(yōu)點。

引言

下變頻器是接收系統(tǒng)中的核心部件,接收系統(tǒng)需要把高頻信號用下變頻器轉(zhuǎn)換到低頻,便于后級進行信號處理。隨著半導體技術的發(fā)展,單片微波集成電路(MMIC) 突破傳統(tǒng)的混合微波集成電路(MIC)快速發(fā)展起來。MMIC 芯片尺寸小,寄生參數(shù)少,具有優(yōu)秀的高頻性能。MMIC 芯片的大規(guī)模運用已成為微波組件小型化的重要途徑之一 。變頻器也向著小型化、高集成、低成本的方向發(fā)展。

本文介紹一種高幅相一致6 ~18 GHz 下變頻器的設計方案和測試結果,該組件采用毫米波變頻方案,幅度和相位都可以數(shù)控調(diào)節(jié)。組件的噪聲系數(shù)優(yōu)于 6 dB,無虛假動態(tài)范圍大于 50 dB,組件之間幅度一致性優(yōu)于±2 dB,相位一致性優(yōu)于±15°。組件內(nèi)部采用多功能芯片,多功能芯片集成了混頻器、倍頻器、低噪聲放大器以及開關。本組件體積小,集成度高,調(diào)試簡單,可以滿足工程應用的需求。

1 下變頻器方案設計

寬帶下變頻器設計要點是在確保噪聲系數(shù)的基礎上,避免帶內(nèi)及近邊帶雜散和虛假信號的產(chǎn)生。根據(jù)下變頻的原理,一個變頻器的雜散水平主要取決于以下兩點:

①射頻帶寬和中頻頻率的比值;

②射頻相對帶寬。具體來說,射頻濾波器組的通道帶寬應盡可能窄,并且要盡量提高中頻的頻率。

下變頻器的噪聲系數(shù)主要取決于射頻前端的增益,較高的前端增益有利于改善噪聲系數(shù); 但是前端增益越大,進入混頻器的信號功率也會增大,容易引起雜散和虛假指標的惡化。在本方案里,可以根據(jù)射頻頻率碼來統(tǒng)籌設置射頻和中頻的衰減值;即總增益保持一定的情況下,在噪聲系數(shù)、虛假和雜散指標之間尋求一個最佳平衡。

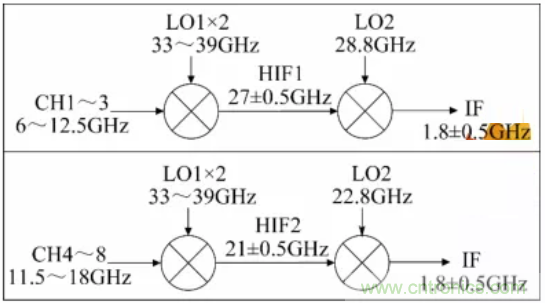

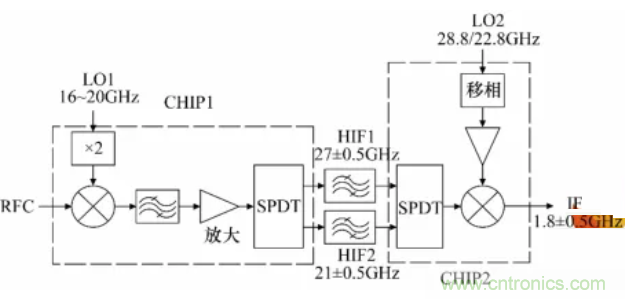

本方案中,考慮到成本和體積,6 ~18 GHz 射頻信號經(jīng)過開關濾波器組劃分為 8 個通道。如圖 1 所示,變頻選擇毫米波本振方案,先將6 ~18 GHz 變頻至 20 GHz 以上的高中頻(HIF1 和 HIF2),再下變頻到低中頻。為確保第一次變頻后的射頻二次諧波不落進帶內(nèi),6 ~12. 5 GHz 和 11. 5 ~18 GHz 分別變換至 27 GHz(HIF1)和 21 GHz(HIF2)高中頻,對應的一本振 LO1 頻率為 33 ~39 GHz。第二次變頻選擇兩個點頻作為二本振 LO2,最終獲得 1. 8 GHz 中頻,瞬時處理帶寬為 1 GHz。本方案中,所有的頻率都不超過 40 GHz,以目前的器件水平都比較易于實現(xiàn)。

圖 1 變頻方案

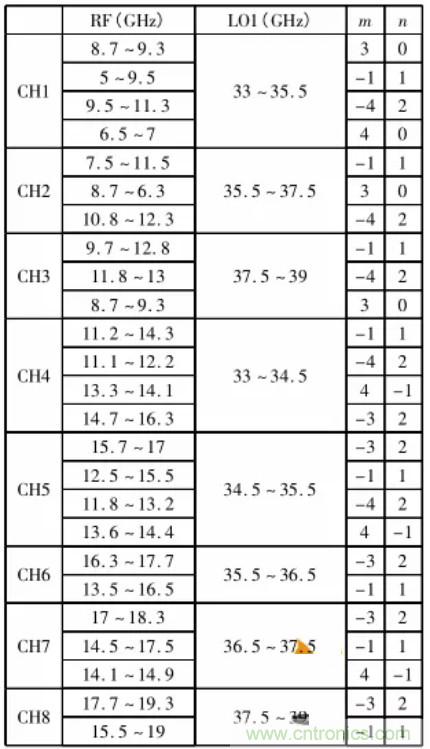

一次混頻雜散計算如圖 2 所示,其中 m 和 n 分別表示射頻和本振的階數(shù)??梢钥闯?,帶內(nèi)及近邊帶沒有小于 3 階的低階雜散。

圖 2 一次混頻雜散分布

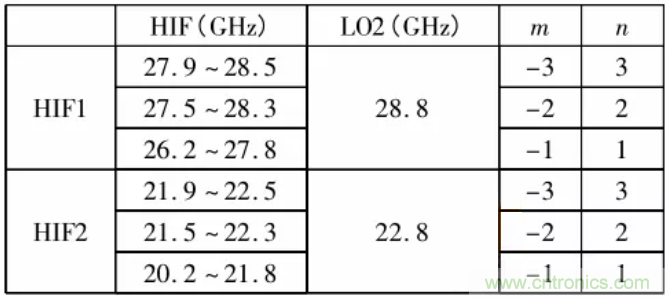

二次混頻雜散如圖 3 所示,只有中頻的二次諧波和三次諧波組合會落入近邊帶,混頻器對這些高階組合的抑制度可以確保虛假和雜散指標。

圖 3 二次混頻雜散分布

上述論證分析表明該變頻方案有效地避開了帶內(nèi)低次雜散。

2 具體電路實現(xiàn)

電路劃分為三部分:射頻前端,變頻電路,中頻電路。下面分別介紹這三部分的電路細節(jié)。

2.1 射頻前端

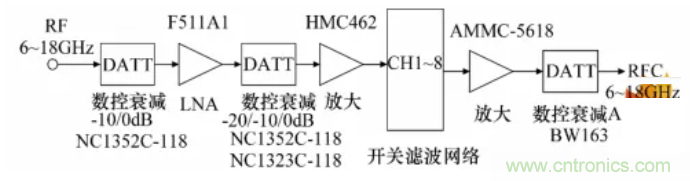

射頻前端部分由低噪聲放大器、數(shù)控衰減器以及 MEMS 開關濾波網(wǎng)絡組成,如圖 4 所示。兩級數(shù)控衰減器,可以將 40 dB 線性動態(tài)范圍擴展為 75 dB全局動態(tài)范圍。射頻前端的設計增益為 14 dB,噪聲系數(shù)為 4 dB,輸入 1 dB 壓縮點為-16 dBm。這里的設計應盡量提高射頻前端的 1 dB 壓縮點,以減小多信號交調(diào),提高系統(tǒng)對多信號的線性處理能力。

圖 4 射頻前端電路

2.2 變頻單元

變頻 單 元 主 要 由 兩 級 多 功 能 芯 片 CHIP1、CHIP2 和兩路濾波器組成,如圖 5 所示。第一級多功能芯片 CHIP1 集成了混頻器、倍頻器、單刀雙擲開關、帶通濾波器以及放大器。第二級多功能芯片CHIP2 集成了混頻器、單刀雙擲開關、移相器以及本振驅(qū)動放大器。二本振設置的移相器用來對同批次不同模塊之間的相位差進行移相補償,以確保模塊之間的相位一致性。如圖 4 所示,電路在混頻前設置了數(shù)控衰減器 A,能夠調(diào)節(jié)進入變頻的信號功率。變頻單元設計增益為-8 dB,噪聲系數(shù)為 11 dB。

圖 5 變頻單元電路

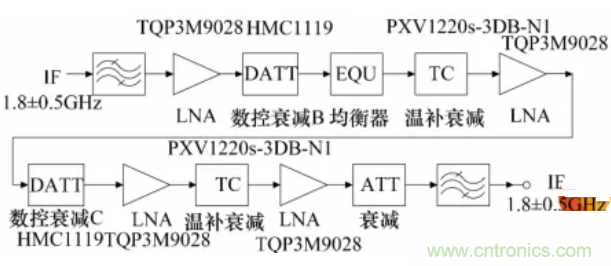

2.3 中頻電路

中頻電路如圖 6 所示。中頻電路主要用來補償增益、濾除雜散信號,并通過均衡器來調(diào)節(jié)中頻帶寬內(nèi)的增益平坦度。數(shù)控衰減器 B 可以和數(shù)控衰減器 A 根據(jù)頻率控制碼進行聯(lián)合作用。數(shù)控衰減器 C用來配合溫度傳感器精確補償增益在環(huán)境溫度下的變化,也可以用來調(diào)節(jié)不同模塊之間的幅度一致性。中頻電路的設計增益為 28 dB,噪聲系數(shù)為 4 dB。

圖 6 中頻電路

根據(jù)上面的設計結果,對級聯(lián)后的系統(tǒng)指標進行了仿真計算。系統(tǒng)總增益為 34 dB,噪聲系數(shù)為5. 25 dB,滿足設計指標的要求。

3 幅相一致性的調(diào)控措施

作為本設計的關鍵指標,幅度一致性是指組件個體之間對應于同一個射頻頻點(等功率輸入)的中頻輸出功率一致性,相位一致性是指組件個體之間對應于同一個射頻頻點(等相位輸入)的中頻相位的一致性。由于射頻頻率被開關濾波器組劃分為8 段,所以從測試結果來看,幅相一致性對應于 8 個射頻頻段的相位一致性。

幅相一致性設計主要靠以下幾點來保證:

①射頻鏈路中的通用器件(MMIC 芯片)需要采購同一批次產(chǎn)品;

②定制器件(MEMS 濾波器、LC 濾波器、腔體濾波器等)需要滿足幅度和相位一致性指標;

③裝配工藝中,所有裝配位置都由制造工藝來定位,而非手工定位。

考慮到工程實際中幅度和相位的差值積累,電路調(diào)試手段不可缺少,本組件中設置有如下措施來調(diào)節(jié)模塊之間的幅相一致性:

①在 LO2 鏈路上設置移相器,用于整體搬移對應的濾波器頻段的相位。因為 LO2 是點頻,對點頻移相不用考慮頻段內(nèi)的相位平坦度。移相器的默認初始移相值為 90°,方便對相位的上下移動調(diào)節(jié)。

②在中頻設置低相移數(shù)控衰減器,用于調(diào)節(jié)各頻段的幅度一致性。低相移的特性可以確保小幅度(≤3 dB)的校正對相位的影響微乎其微(≤2°)。

4 實物及測試結果

圖 7 為變頻單元測試板,兩級變頻芯片之間采用基片集成波導(SIW)濾波器。

圖 7 變頻單元測試板

變頻器的實物尺寸為 130 mm×80 mm×20 mm,如圖 8 所示。

圖 8 下變頻器實物圖

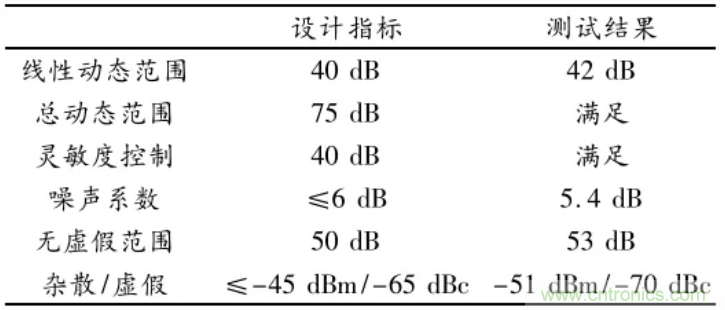

同批次模塊測試結果(除幅相一致性指標外)見表 1,測試結果達到了設計指標的要求。

表 1 測試指標與設計指標對照表

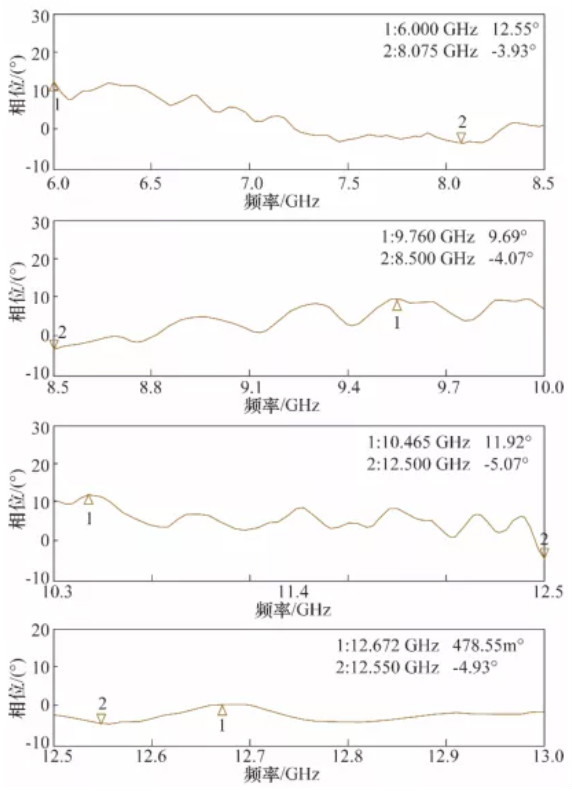

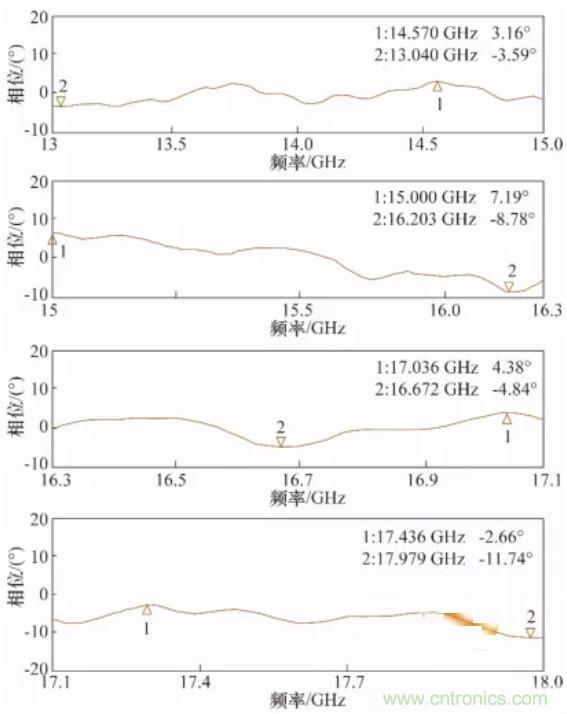

同批次模塊的相位一致性測試曲線如圖 9 所示,自上而下依次為 8 個射頻通道的相位一致性測試曲線,可以看出,相位差值均在 20°以內(nèi),達到了設計指標(優(yōu)于±15°)的要求。

圖 9 相位一致性測試曲線

同批次模塊的幅度一致性測試曲線如圖 10 所示,該曲線為 6 ~18 GHz 范圍內(nèi)的射頻頻點對應的1. 8 GHz 中頻幅度差值??梢钥闯觯炔钪稻?. 5 dB 以內(nèi),達到了設計指標(優(yōu)于±2 dB)的要求。

圖 10 幅度一致性測試曲線

5 結論

本文介紹了一種高幅相一致6 ~18 GHz 下變頻器的設計方案和測試結果。組件內(nèi)部采用多功能芯片,片上集成了混頻器、倍頻器、低噪聲放大器以及開關。測試結果表明,組件的無虛假動態(tài)范圍大于50 dB,噪聲系數(shù)優(yōu)于 6 dB,幅度一致性優(yōu)于±2 dB,相位一致性優(yōu)于±15°。本組件體積小,本組件體積小,集成度高,易于調(diào)試,可以滿足工程需要。(參考文獻略)

作者:張得才 管 飛 吳志亮 王洪林 陳 坤

推薦閱讀: