【導(dǎo)讀】除了簡單的攝影和顯示,3D擴增實境技術(shù)也用盡了CMOS技術(shù)的所有潛能,提供另類的視覺空間體驗。一如地球上的主要物種,CMOS傳感器已經(jīng)大大進(jìn)化并適應(yīng)其周遭環(huán)境。

I. 引言

早于上世紀(jì)九十年代初,有意見認(rèn)為電荷耦合器件(Charge Coupled Device,CCD) 日漸式微,最終將成為“科技恐龍”。如果用索尼公司(Sony) 2015年的發(fā)布來看待,這個預(yù)言好像也有點道理:當(dāng)時索尼公司正式發(fā)布終止量產(chǎn)CCD 時間表,并開始接收最后訂單。雖然多年前業(yè)界已預(yù)計這是遲早出現(xiàn)的舉措,但是索尼這一發(fā)布仍然震驚了專業(yè)成像社群。值得一提的是很多工業(yè)或?qū)I(yè)應(yīng)用(就是CMOS 圖像傳感器 (CIS) 的重點市場)到現(xiàn)在仍然基于CCD傳感器技術(shù)。到底CCD有什么特點優(yōu)于CIS,使其更具吸引力呢?在發(fā)展初期,CCD和CIS兩種技術(shù)是共存的;后來CCD被視為能夠滿足嚴(yán)格圖像質(zhì)量要求的高階技術(shù),而同時期的CMOS技術(shù)仍然未成熟并受制于其固有噪聲和像素復(fù)雜性等問題。在這一時期,圖像技術(shù)仍然以模擬結(jié)構(gòu)為主,而集成圖像處理功能(系統(tǒng)級芯片SOC) 這一意念還沒有被認(rèn)真考量?;谀柖?,技術(shù)節(jié)點的縮小使得SOC技術(shù)從2000年起快速擴展并更具競爭力。現(xiàn)在CIS繼續(xù)致力改進(jìn)光電性能,在很多方面都顯得比CCD優(yōu)勝。如果利用文首提到的“進(jìn)化論”譬喻,其實可以把CIS視作抵過多次自然災(zāi)害仍然存活的哺乳類動物,而這個進(jìn)化歷史更是跨越6500萬年的史詩式故事!

II. CCD 和 CMOS:同源異種

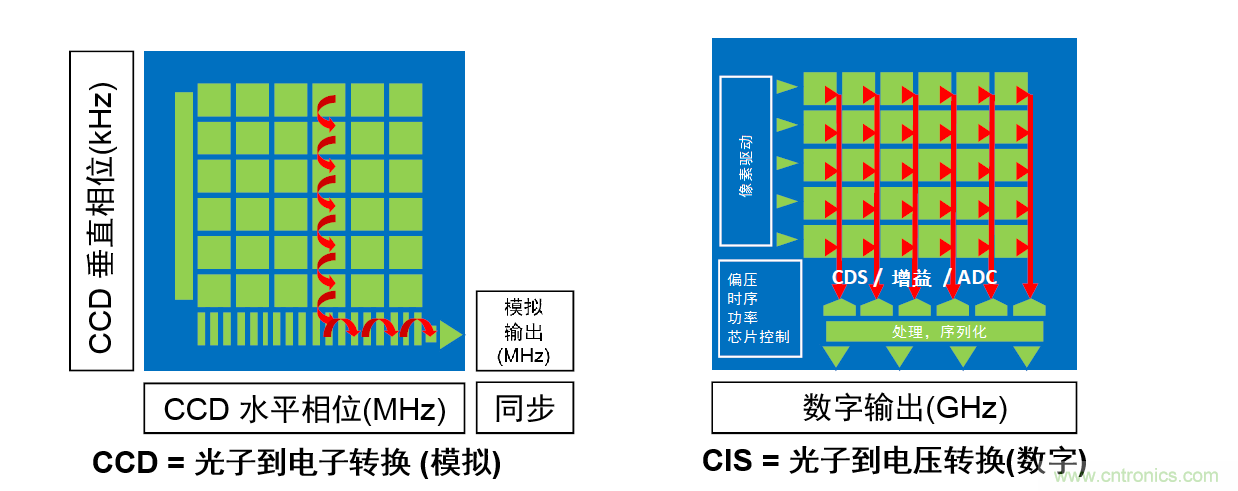

CCD的工作原理是將光子信號轉(zhuǎn)換成電子包并順序傳送到一個共同輸出結(jié)構(gòu),然后把電荷轉(zhuǎn)換成電壓。接著這些信號會送到緩沖器并存儲到芯片外。在CCD應(yīng)用中,大部分功能都是在相機的電路板上進(jìn)行的。當(dāng)應(yīng)用需要修改時,設(shè)計人員可以改動電路而無需重新設(shè)計圖像芯片。在CMOS圖像傳感器中,電荷轉(zhuǎn)換成電壓的工作是在每一像素上進(jìn)行。CMOS圖像芯片在像素級把電荷轉(zhuǎn)換成電壓,而大部分的功能則集成進(jìn)芯片。這樣所有功能可通過單一電源工作,并能夠?qū)崿F(xiàn)依照感興趣區(qū)域或是開窗靈活讀出圖像。 一般來說,CCD採用NMOS技術(shù),因而能夠通過如雙層多晶硅、 抗暈(antiblooming)、金屬屏蔽和特定起始物料互相覆蓋等特定工藝實現(xiàn)性能。而CMOS是基于用于數(shù)字集成電路的標(biāo)準(zhǔn)CMOS工藝技術(shù)生產(chǎn),再根據(jù)客戶要求加入成像功能(如嵌入式光電二極管) 。

一般的見解是CMOS傳感器的生產(chǎn)成本比CCD低,因而它的效能也較CCD低。這個假設(shè)是基于市場需求的考量而出的,但是其它專業(yè)市場的意見卻認(rèn)為兩者的技術(shù)水平相若,而CCD甚至可能更經(jīng)濟[3]。例如大型主要的航天計劃仍然採用CCD元件,原因不單是CCD在小批量和低成本的考量下在工藝級實現(xiàn)性能優(yōu)化,還有是長期穩(wěn)定供貨的需求考量。同樣地,基于高端CCD的解決方案在科學(xué)成像市場也有主流占有率,而且還有一些新產(chǎn)品在開發(fā)階段。情況就是恐龍進(jìn)化成飛鳥,而它們大部分都能夠提供優(yōu)秀的成像功能……

CMOS的擁有經(jīng)改進(jìn)的系統(tǒng)復(fù)雜性,因為它基本上是嵌入了如模數(shù)轉(zhuǎn)換、相關(guān)雙采樣(CDS)、時鐘生成、穩(wěn)壓器等系統(tǒng)級芯片(System-On-Chip,SOC)結(jié)構(gòu),或是影像后處理等功能,而這些以前都是應(yīng)用系統(tǒng)

級設(shè)計才有的功能。現(xiàn)在的CIS通常是依照從180 nm到近期65 nm的1P4M (1層聚酯,4層金屬) 工藝生產(chǎn),允許像素設(shè)計加入非常高的轉(zhuǎn)換因子,便于結(jié)合列增益放大。這使得CMOS的光反饋和光敏感度一般都比CCD為佳。相較于CMOS,CCD芯片的襯底偏壓穩(wěn)定性更好且芯片上的電路更少,所以擁有更顯著的低噪優(yōu)勢,甚至達(dá)到無固定模式噪聲的水平。

圖1 – CCD 和 CMOS 結(jié)構(gòu)比較表

表 1 – CCD-CMOS 特點比較表

另一方面,CIS有較低采樣頻率,可以減小像素讀出所需要的帶寬,因而瞬時噪聲也較小??扉T會同時對陣列上的所有像素進(jìn)行曝光。但是CMOS傳感器采用這一方法的話,由于每像素需要額外的晶體管,反而占用更多像素空間。另外,CMOS每一像素?fù)碛幸粋€開環(huán)輸出放大器,而因著晶圓工藝的差異,每一放大器的補償和增益會有所變化,使高或暗的不均勻狀況都比CCD傳感器差。相對于同級的CCD傳感器,CMOS傳感器擁有較低的功耗,而芯片上其它電路的功耗也比CCD經(jīng)優(yōu)化模擬系統(tǒng)芯片匹配的解決方案來得低。取決于供貨量并考慮到CCD導(dǎo)入外部相關(guān)電路功能的成本,CMOS的系統(tǒng)成本也有可能低于CCD。表一總結(jié)了CCD和CMOS的特點,有些功能有利于一種或其他技術(shù),所以毋需完全分割整體性能或成本。不過,CMOS的真正優(yōu)勢是通過系統(tǒng)級芯片(system-on-chip)方式實現(xiàn)導(dǎo)入靈活性,以及其低功耗特點。

I. 關(guān)于噪聲性能的常見誤解

視頻成像鏈的帶寬必需小心調(diào)整,以便最小化數(shù)字化階段的讀出噪聲??墒沁@一帶寬也必需足夠大以防止圖像出現(xiàn)其他缺陷。這一慣常做法也適用于CCD和CMOS。帶寬的最小閾值是信號由采樣達(dá)到足夠接近理想水平所需要的時間決定。誘發(fā)性錯誤應(yīng)處于接近最低有效位(Least Significant Bit,LSB) 的可忽略水平。要決定所需要的帶寬,可以應(yīng)用下面的準(zhǔn)則:

把放大鏈帶寬fc,信號頻率fs和N(即ADC解析率)置入算式計算。例如N=12時,數(shù)值則是:

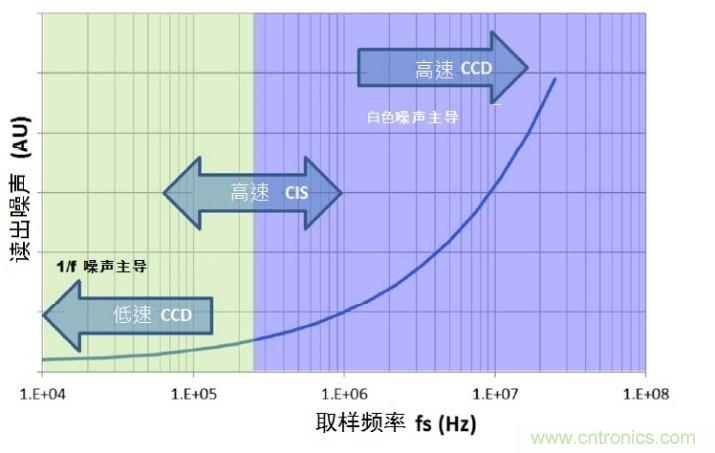

噪聲最由兩個因素造成:1/f閃爍噪聲和熱噪聲(見圖2)。閃爍噪聲是大自然中常有的噪聲,而它旳頻譜密度和地球自轉(zhuǎn)速度、海底水流、天氣以至氣候現(xiàn)象等活動相關(guān)。研究報告顯示普通蠟燭的閃爍速率是1/f 。在MOS器件和放大鏈各元素中,閃爍噪聲則是技術(shù)工藝誤差生成的缺陷,使電荷被困于柵極氧化物內(nèi)所造成的結(jié)果。電荷進(jìn)出這些“陷阱”,造成晶體管通道內(nèi)的電流不穩(wěn)定 [6],故又稱「隨機電報噪聲」(random telegraph noise,RTS)。利用洛倫茲數(shù)學(xué)模型(Lorentzian mathematical model) 可以形容每一個“陷阱”的共振行為,而模型的總和(即MOSFET通道表面范圍的所有“陷阱”總和)在1/f頻譜上展示時,會全完符合具體噪聲的頻譜密度。結(jié)果顯示,1/f波幅與MOSFET通道表面面積成反比──而不是完全直觀。

圖2 – 頻譜噪聲密度

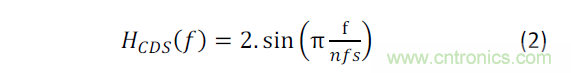

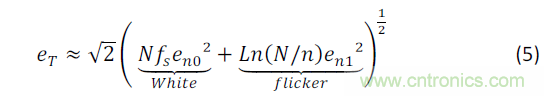

要去除或減小CIS上的放大器共模差異,浮點的重置噪聲以至晶體管技術(shù)分散,視頻通道通常集成一個相關(guān)雙采樣(CDS)級。這一元素把視頻信號傳送函數(shù)依照下面的算式進(jìn)行轉(zhuǎn)換:

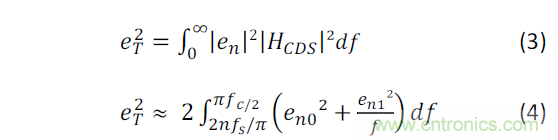

在算式中,fs 是采樣頻率, n是CDS 因子(通常n=2)。如圖3顯示,取決于采樣頻率,這一濾波或多或少地去除1/f噪聲頻率成分,尤其是當(dāng)采樣頻率fs很高的時候 顯著(換句話說,電荷進(jìn)出“陷阱”的動作將慢于CDS頻率)。HCDS濾波器結(jié)合放大鏈的低通濾波器可以簡化為一個如圖3所示的等效帶通濾波器。圖中的eqBP1 對應(yīng)一個一級帶通濾波器。這裡eqBP1的噪聲頻譜函數(shù)要除以2,以得到一個帶有HCDS函數(shù)的等效集成噪聲功率 。eqBP2 是eqBP1的陷波估算值。要取得集成噪聲功率,eqBP2 的上限和下限分別按照下列算式進(jìn)行倍增:

圖3 – 噪聲濾波函數(shù)

在圖2和圖3所示的一般狀況下,噪聲性能可依照下面的算式展示:

把算式(1) 和 (4) 合并后,得出總體集成讀出噪聲估算值如下:

有關(guān)算式經(jīng)驗證跟數(shù)字仿真結(jié)果相當(dāng)匹配。CCD的讀出噪聲可達(dá)到非常低水平,適合如天文或科學(xué)成像,這些應(yīng)用領(lǐng)域的讀出頻率可以非常低。

系統(tǒng)設(shè)計包含有最小頻帶寬的電子元素,以避免集成進(jìn)信號的不穩(wěn)定時脈。在這些應(yīng)用中,噪聲的1/f元件有主導(dǎo)地位。在高速視頻應(yīng)用中, 高噪聲使得信噪比顯著變差。從多個不同CCD視頻相機錄得的具體噪聲表示狀況數(shù)據(jù),確認(rèn)了有關(guān)理論 [5] 。CMOS 圖像傳感器的列式平行讀出布局(見圖一)在這一方面提供優(yōu)勢。閾值讀出頻率除以列數(shù),再與CCD數(shù)值比較。在這裡,CIS的讀出噪聲主要由1/f數(shù)值主導(dǎo)。這有助于進(jìn)一步改進(jìn)CMOS技術(shù)在成像方面的性能。近期的結(jié)果顯示,CIS可提供達(dá)到1E-或更低范圍的優(yōu)秀噪聲性能。

圖4 – 讀出噪聲作為fs的函數(shù)

II. MTF 和 QE:成像質(zhì)量的支柱

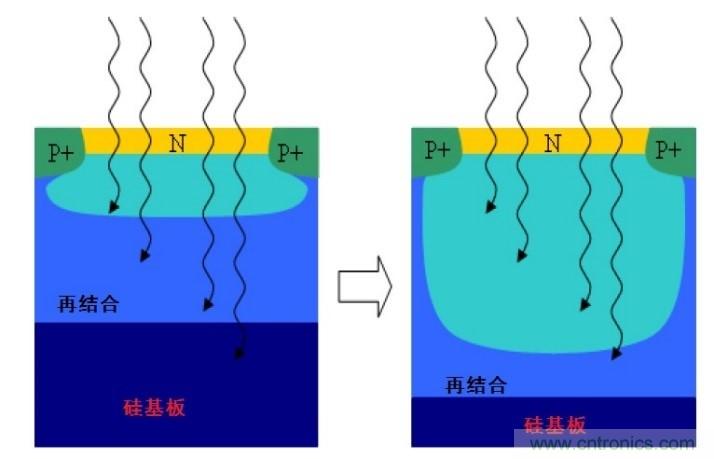

量子效率(Quantum efficiency ,QE) 是直接影響圖像傳感器光電性能的因素,因為光電轉(zhuǎn)換效率的任何損耗都會直接減低信噪比 (Signal-To-Noise- Ratio,SNR) 。它的影響是兩方面的,因為當(dāng)散粒噪聲(信號的平方根)是主要噪聲源時,QE不單是信噪比的被除數(shù)(信號),同時也是除數(shù)(噪聲)。在這一點之上,CCD和CMOS處于同一水平,可是CCD在QE改進(jìn)方面累積有多年的技術(shù)工藝優(yōu)化,而在CIS的QE改進(jìn)發(fā)展相對較遲?;诠栉镔|(zhì)的物理特性,較長的波長能穿透光敏轉(zhuǎn)換地帶,所以會使用厚的外延材料來增加上紅色和近紅外線波長的QE。根據(jù)比爾朗伯定律(Beer-Lambert law),被吸收的能量是與介質(zhì)的厚度成指數(shù)關(guān)係。高端應(yīng)用的 CCD 利用較厚的硅物質(zhì)和背照(back side illumination ,BSI)工藝以恢復(fù)高寬帶QE和近紅外線(near infrared ,NIR)敏感度,因而擁有優(yōu)勢。

圖5 – QE 指標(biāo)

隔行傳輸CCD(interline transfer CCD,ITCCD) 是基于特定的生產(chǎn)工藝,導(dǎo)入所謂的“垂直溢漏”(vertical overflow drain,VOD)或“垂直抗暈”(vertical antiblooming,VAB)功能。VAB開發(fā)于1980年代初期,具有非常好的性能,但缺點是會減低紅色的反饋并拒絕頻譜中的NIR部份。

圖 6 – 深耗盡方法

因為這個原因,ITCCD不能從BSI中獲益。而高端CCD因為使用垂直抗暈工藝,所以沒有這一限制。而CMOS也具有同一特點:在薄的感測層上,因為電荷不會在像素之間滲透,所以沒有串?dāng)_的缺點。結(jié)果是ITCCD和標(biāo)準(zhǔn)CIS都能夠?qū)崿F(xiàn)良好的空域解析度或調(diào)制轉(zhuǎn)換函數(shù)(modulated transfer function,MTF) 。要增加NIR部份和敏感度,需要顯著增加物料厚度,但是厚物料會增加光電串?dāng)_,引致MTF衰減。成像質(zhì)量是MTF和QE的綜合結(jié)果(即所謂的檢測量子效率Detective Quantum Efficiency,DQE),所以必需同時考量空域和時域因素。圖6顯示利用硅摻雜方法恢復(fù)MTF的深耗盡(deep depletion)光電二極管。一般來說,CIS使用類似集成電路的常用技術(shù)(特別是DRAM/內(nèi)存工藝)生產(chǎn),所以不會牽涉上述的特定工藝配方。不過近期的技術(shù)研究文章展示適用于CIS的特定工藝導(dǎo)入方案,能實現(xiàn)出色的QE改進(jìn)甚至相對接近高端CCD的水平(見圖5)。最新的CMOS技術(shù)趨勢可說是突飛猛進(jìn),引進(jìn)了如導(dǎo)光板、深槽隔離(deep trench isolation,DTI)、埋藏微透鏡,以及在光敏范圍下嵌入包含像素晶體管的迭層芯片等技術(shù)。

III. 固有缺陷

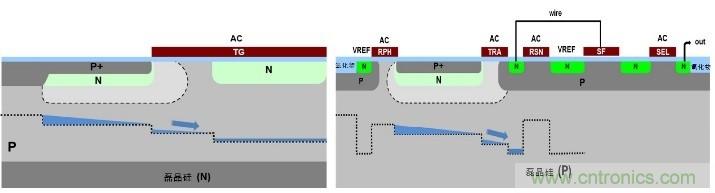

“嵌入式光電二極管” (pinned photodiode,PPD) 或“空穴堆積二極管”(hole accumulation diode,HAD) 最初開發(fā)目的是消除延遲并把全部電荷從光電二極管轉(zhuǎn)移到ITCCD寄存器[12]。CMOS圖像傳感器的一個重大發(fā)展是在2000年代初期引進(jìn)ITCCD光電二極管結(jié)構(gòu)[11],如圖7所示。在CMOS中,像素結(jié)構(gòu)多數(shù)以每像素的晶體管數(shù)目來表示。大部分 CMOS圖像傳感器傾向使用電子卷簾快門(electronic rolling shutter),這有助于集成并只需少至三個晶體管 (3T)就能實現(xiàn)。雖然有結(jié)構(gòu)簡單的優(yōu)點,3T像素結(jié)構(gòu)的缺點是電路來自kT/C (或溫度) 噪聲的像素生成時域噪聲會較大,而且不能輕易消除。

圖 7 – ITCCD 和 5T CMOS 圖像對比圖

嵌入式光電二極管最初引進(jìn)到CIS以去除來自浮動擴散重置的噪聲,后來并引進(jìn)到四晶體管像素(4T)結(jié)構(gòu)中。4T結(jié)構(gòu)進(jìn)行相關(guān)雙采樣(CDS)以消除重置瞬時噪聲。這一結(jié)構(gòu)也允許晶體管在像素間共用布局,以便于把每像素的有效晶體管數(shù)目減到兩個或更少。事實證明,每像素的晶體管數(shù)目減少,能夠空出更多范圍供光敏部分或填充因子去更直接地把光線耦合到像素上。不過如圖8所示,在擷取視頻或包含快動作的圖像時,ERS會導(dǎo)致更多圖像變形。PPD會在第二級時工作,以進(jìn)行全局快門(GS)擷取。它能夠去除ERS偽影并進(jìn)一步消除時域噪聲、暗電流和固定模式噪聲。接近PPD的第五個晶體管(5T)的功能是排除過多的電荷并調(diào)整重迭模式的集成時間(在集成時讀出)。

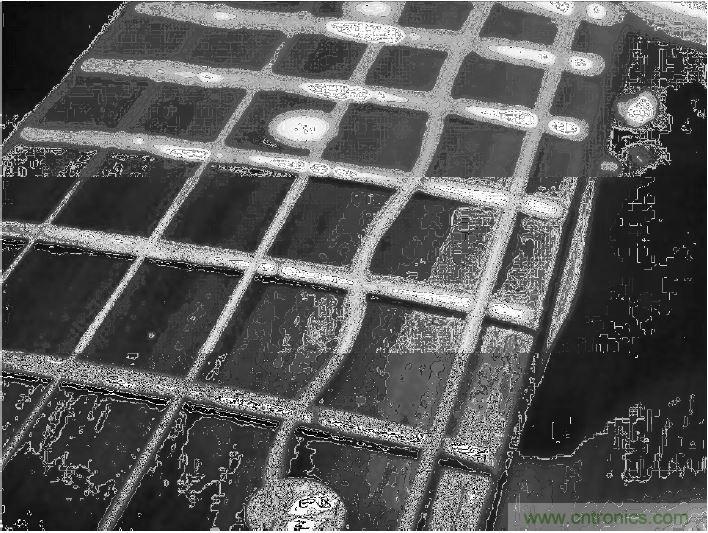

圖 8 – 圖像瑕疵:CMOS ERS 變形

全局快門(GS)模式一般配合 ITCCD使用,但在某些狀況下會對彌散現(xiàn)像敏感。

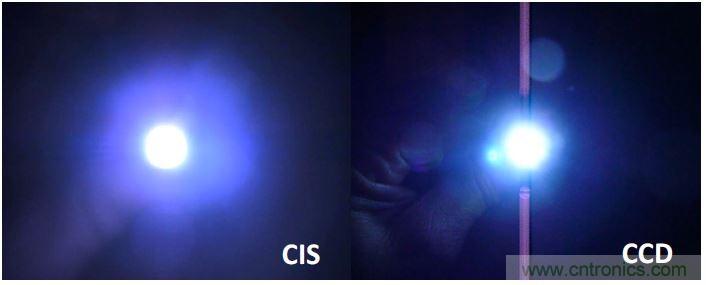

圖 9 – 圖像瑕疵:CCD 彌散

彌散是在電荷轉(zhuǎn)移時出現(xiàn)的現(xiàn)像,會在影像上產(chǎn)生直線如圖9。這瑕疵在高反差圖像上尤其顯著,但不應(yīng)把它和相似的光暈現(xiàn)像混淆。最常用的解決方案是導(dǎo)入幀行間轉(zhuǎn)移(frame-interline transfer,F(xiàn)IT) CCD結(jié)構(gòu),而FIT也擁有較高視頻速率的優(yōu)點。與CMOS等效的彌散參數(shù)是全局快門效率(Global Shutter Efficiency,GSE) ,

有時也稱為寄生光敏度(parasitic light sensitivity,PLS) ,是對應(yīng)于傳感節(jié)點到光電二極管的敏感度比例。ITCCD 的GSE 值一般介乎于-88dB 到 -100dB [13],在CMOS則是-74dB 到 -120dB 甚至是3D迭層結(jié)構(gòu)的 -160dB 。利用先進(jìn)訂製像素微鏡片(如zerogap) 可在從改進(jìn)波長反饋的敏感度到減小CMOS像素上的二極管所造成的填充因子損失方面實現(xiàn)顯著的分別。它也是改進(jìn)GSE性能的主要因素。

IV. CMOS 成像技術(shù)的未來

CCD技術(shù)特別適合時間延遲積分(time delay integration,TDI)領(lǐng)域。TDI(在掃描場景時,電子同步的積分和累加)的導(dǎo)入相對直接,只需要一個電荷轉(zhuǎn)移器件就可以完成。這技術(shù)最初用于信噪比最大化,然后用于CIS CCD以保存良好的圖像定義(MTF)。近年多個于模擬區(qū)域(電壓) 或數(shù)字區(qū)域復(fù)製信號累加的嘗試,為CMOS TDI開拓新的發(fā)展方向。不論在太空地面觀測或是在機器視覺方面,CCD延遲積分結(jié)構(gòu)的低噪聲和高敏感度性能都廣受歡迎。不過現(xiàn)時最令人期待的發(fā)展是基于CMOS工藝、但擁有CIS CCD的優(yōu)點以及電荷轉(zhuǎn)移寄存器結(jié)合行式ADC轉(zhuǎn)換器的技術(shù) 。雖然有長足進(jìn)步,CMOS圖像傳感器的敏感度在光線非常微弱應(yīng)用(如只有幾十微流明的環(huán)境) 仍然受限于讀出噪聲。使用電子倍增技術(shù)的EMCCD 顯示出在降噪方面的巨大潛力,因而受到科學(xué)成像市場的注意。一般來說,就如 CCD被CMOS 傳感器取代一樣, EMCCD 也有潛力朝著電子倍增CMOS (electron multiplying CMOS,EMCMOS)的方向發(fā)展[20]。一如EMCCD,EMCMOS計劃改進(jìn)光線非常微弱應(yīng)用中的圖像質(zhì)量,以配合科學(xué)或監(jiān)視方面的應(yīng)用。CMOS 技術(shù)有助于實現(xiàn)更小更具智能的系統(tǒng)、降低功耗,以減低量產(chǎn)的成本。(即所謂的 SWAP-C 方法)。電子倍增的原理是在讀出鏈任何加入任何噪聲前為信號進(jìn)行增益,使得噪聲被增益攤分,以改進(jìn)信噪比。基于CCD原理,信號會以電子包的形式傳送,然后在讀出之前共同對每一個像素進(jìn)行倍增。CMOS的信號是在電壓域,因而倍增工作必需在源跟隨晶體管把噪聲加進(jìn)信號并傳送到浮點之前完成。

隨著3D成像的流行,需要物件深度的信息,飛行時間(Time-Of-Flight,TOF)技術(shù)在這一方面派上用場。TOF的原理是在傳感器平面上設(shè)置人工脈沖光源并發(fā)射出去,然后把反饋的反射波段用于相關(guān)函數(shù)計算來得出距離。這一技術(shù)于1995年于 “鎖定”CCD中首次提。而TOF在CMOS的應(yīng)用則是由CCD像素的啟發(fā)而來。另一方法則是使用電流輔助光子解調(diào)器(Current Assisted Photonic Demodulators,CAPD)測量深度。兩種方法都實現(xiàn)了工業(yè)3D傳感器的量產(chǎn)并實現(xiàn)了一系列的應(yīng)用如計算人數(shù)、安全監(jiān)控、計量學(xué)、工業(yè)機器人、手勢辨識和先進(jìn)汽車駕駛者輔助系統(tǒng) (ADAS)等。這是都是CCD技術(shù)衍生的意念成功過度到CMOS作改進(jìn),再實現(xiàn)工業(yè)應(yīng)用大規(guī)模導(dǎo)入的典型例子。

CMOS 技術(shù)導(dǎo)入也衍生出新的應(yīng)用范圍。舉個例子,跟CCD在1980年代在專業(yè)相機領(lǐng)域替代現(xiàn)像管(vidicon tubes)相似,單光子雪崩二極管(Single- Photon Avalanche Diode,SPAD) 原來的開發(fā)目的是作為光電倍增管(photomultiplier tubes,PMT)的固態(tài)替代產(chǎn)品。SPAD基本上是在所謂的蓋革模式(Geiger mode)中,依照擊穿模式上的反壓進(jìn)行偏置的p-n 結(jié)。不過這結(jié)構(gòu)十分不穩(wěn)定,任何能量改變都會導(dǎo)致雪崩效應(yīng)。這一特點被用于單光子感測。通過在SPAD和輸入電壓之間導(dǎo)入一個簡單的電容元件,利用被動抑制原理開閉雪崩,或使用嵌入式MOSFET通道啟動主動抑制原理達(dá)到同一目的。這樣就可以製作代表量子事件的數(shù)字信號。根據(jù)原理,SPAD 一個基于簡單結(jié)構(gòu)的CMOS技術(shù),無需用于圖像傳感器的專門工藝。不過因為它需要復(fù)雜的電路,SPAD陣列的工作也較為復(fù)雜。跟光子的到達(dá)一樣, SPAD的引發(fā)和事件記數(shù)依定義是非同步的。CMOS技術(shù)因而是不二之選。例如這就能夠非??焖俚貑訏呙柘袼仃嚵?,以確認(rèn)已轉(zhuǎn)換的像素。這些幀組合后就能製作一個視頻序列 [23]。

V. 總結(jié)

早期一些宣稱CCD年代終結(jié)的文章已被視為預(yù)言,只是實際的過渡時間比預(yù)計的長許多。另一方面開發(fā)用于CMOS圖像傳感器的圖像結(jié)構(gòu)種類和創(chuàng)新性都大大超越前人想像。隨著晶體管蝕刻工藝縮小化和CMOS生產(chǎn)技術(shù)演進(jìn),這些創(chuàng)新都變得可行。大型工業(yè)成像廠商除了價格,還繼續(xù)在光電性能方面進(jìn)行競爭。現(xiàn)在的使用者已經(jīng)不是單單在乎于拍照,而是擷取人生中各個重要時刻,因而期待不論在任何光線狀況下都能拍出完美的照片。工業(yè)應(yīng)用也因著這些改進(jìn),在其它一般范圍上得益。越來越多視覺系統(tǒng)也基于消費者市場趨勢而調(diào)整其圖像傳感器要求,圖像縮小就是一個例子。而高速處理能夠提升高成本生產(chǎn)機器的產(chǎn)量并實現(xiàn)自動化工藝和檢查,所以也是一個重要的經(jīng)濟因素。新的應(yīng)用正把傳感器推向性能極限并不允許圖像內(nèi)有更多噪聲,推動了單光子成像技術(shù)。除了簡單的攝影和顯示,3D擴增實境技術(shù)也用盡了CMOS技術(shù)的所有潛能,提供另類的視覺空間體驗。一如地球上的主要物種,CMOS傳感器已經(jīng)大大進(jìn)化并適應(yīng)其周遭環(huán)境。

推薦閱讀: